TSMC Technology Symposium: Feuer aus allen Rohren: N3, N4, N5HPC, N6, N7HPC und mehr

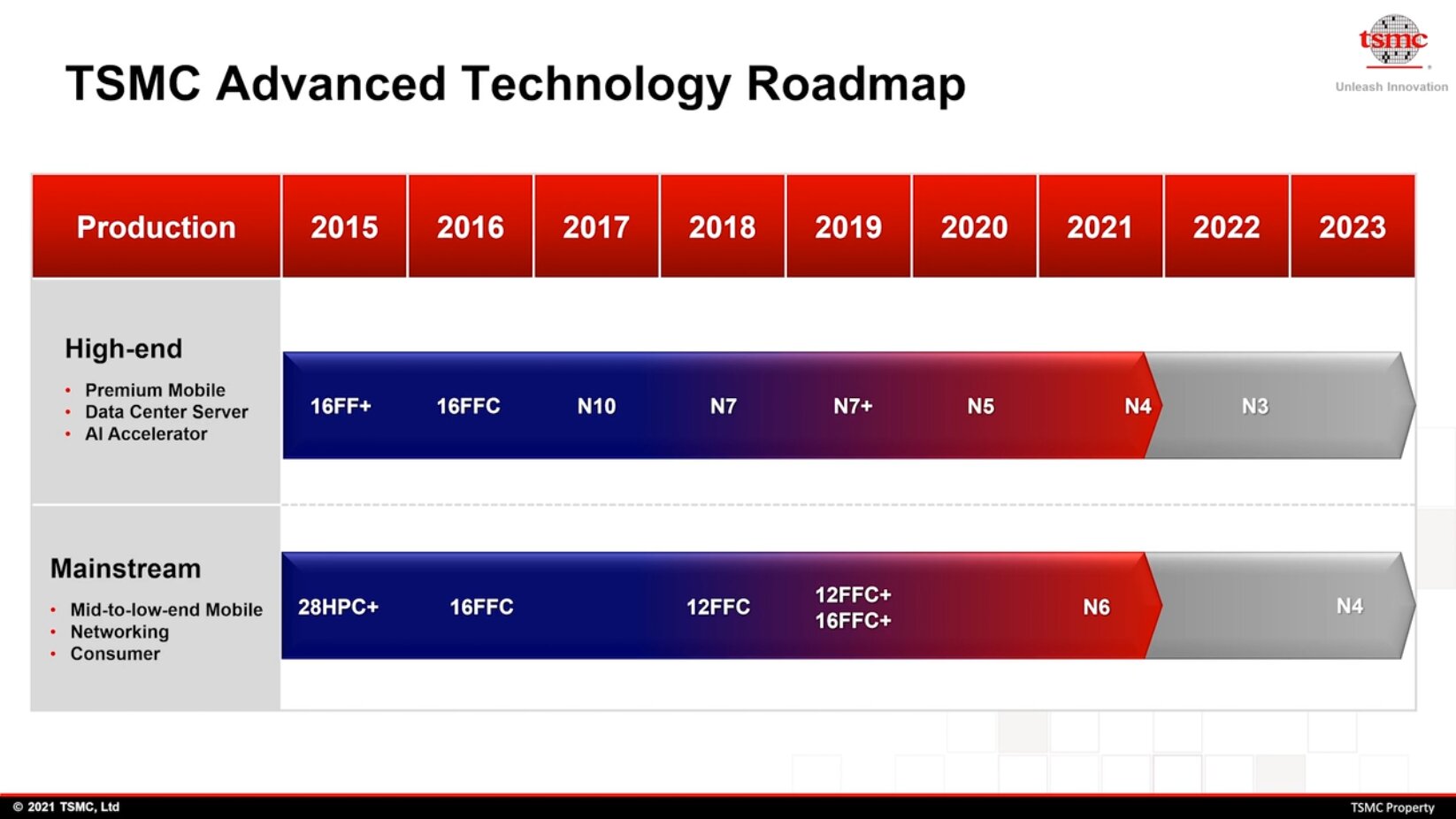

TSMCs Technology Symposium gibt detaillierte Einblicke in den aktuellen Stand der Forschung und Entwicklung von 6 bis 2 nm und zeigt viele Zwischenstufen, die auf dem Weg dahin genutzt werden können. TSMC stellt dabei glasklar, dass sie nie eigene Produkte bauen werden, sondern der vertrauenswürdige Partner für alle sein wollen.

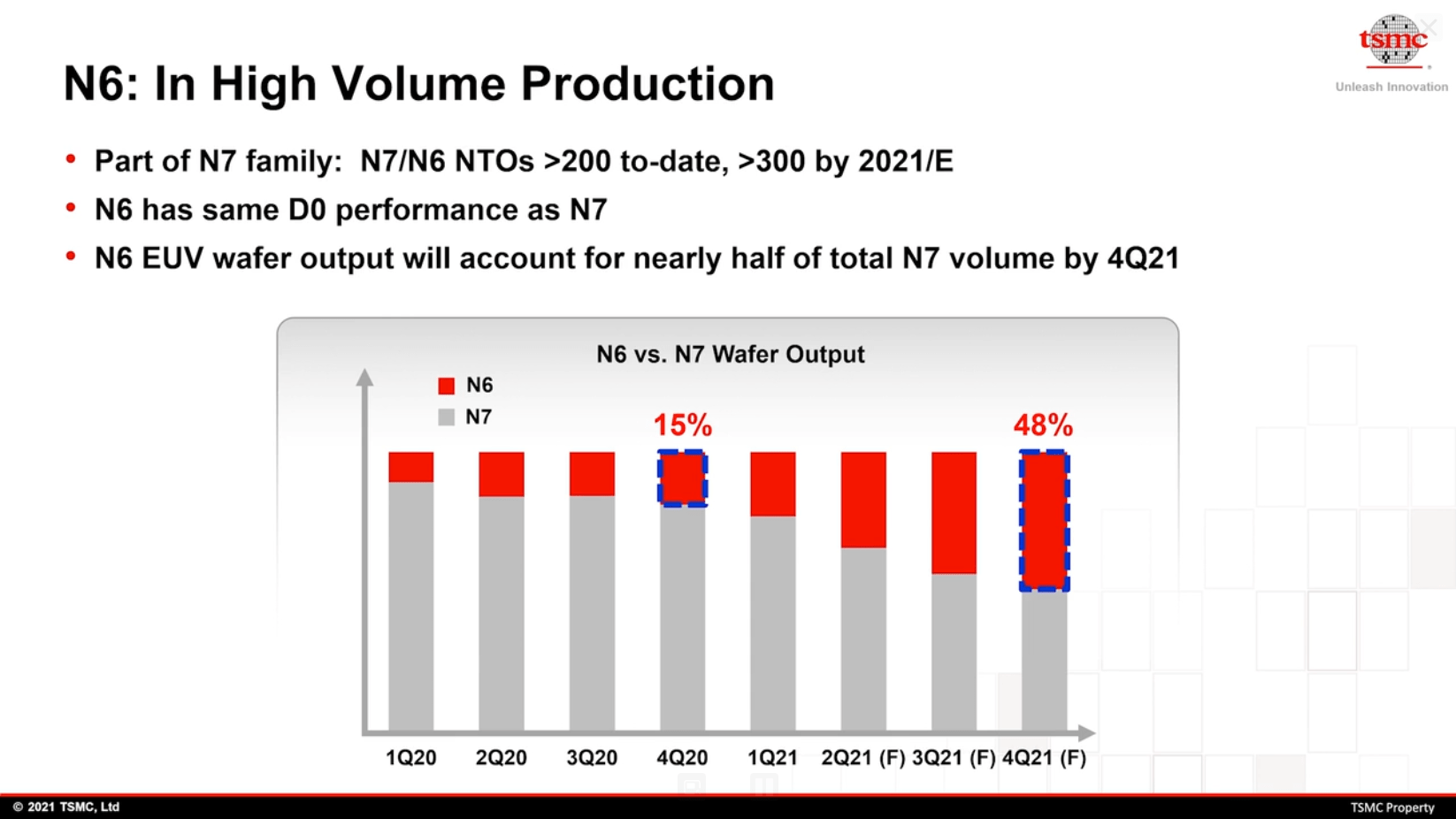

6 nm läuft 7 nm bald den Rang ab

Die überraschendsten Aussagen traf TSMC dabei zur 6-nm-Fertigung N6. Diese nimmt derzeit einen rapiden Aufstieg im Konzern, zum Ende des Jahres soll sie mit N7, also der klassischen 7-nm-Fertigung, bereits gleichgezogen haben.

N6 profitiert davon, der große Schritt für den Mainstream-Markt zu sein, der zum Teil bisher noch mit 16- oder 12-nm-Chips beliefert wurde. N6 ist deshalb kein eigentlicher Nachfolger von N7, sondern eher ein Schritt zur Seite für einen anderen Markt. Das Gros der Kundschaft kommt aus dem mobilen Bereich, diese profitiert von 18 Prozent gesteigerter Dichte und zusätzlichen EUV-Belichtungsschritten gegenüber N7. Der Vergleich zu 16 oder 12 nm ist natürlich noch viel größer.

Mit N6RF wird zudem gleich eine Spezialversion abgezweigt, die für den 5G-Markt und moderne Wi-Fi-Lösungen optimiert ist. Je nach Einsatzgebiet ist der Sprung groß, denn auch hier kommen Chips noch aus einer vergleichsweise viel älteren Fertigungsstufe.

Höchstleistung mit N7HPC und N5HPC

Der N7-Prozess ist mit den stetigen weiteren Entwicklungen aber noch nicht tot. Mit N7HPC wird bereits in wenigen Monaten eine verbesserte Variante der 7-nm-Fertigung zur Verfügung stehen, die bis zu zehn Prozent mehr Leistung auch dank mehr Leistungsaufnahme ermöglichen wird. N5HPC folgt im kommenden Jahr als verbesserte N5-Variante für das HPC-Segment. Es ist das erste Mal seit einem 22-nm-Prozess, dass TSMC wieder einen Spezialprozess für höchste Leistung auflegt.

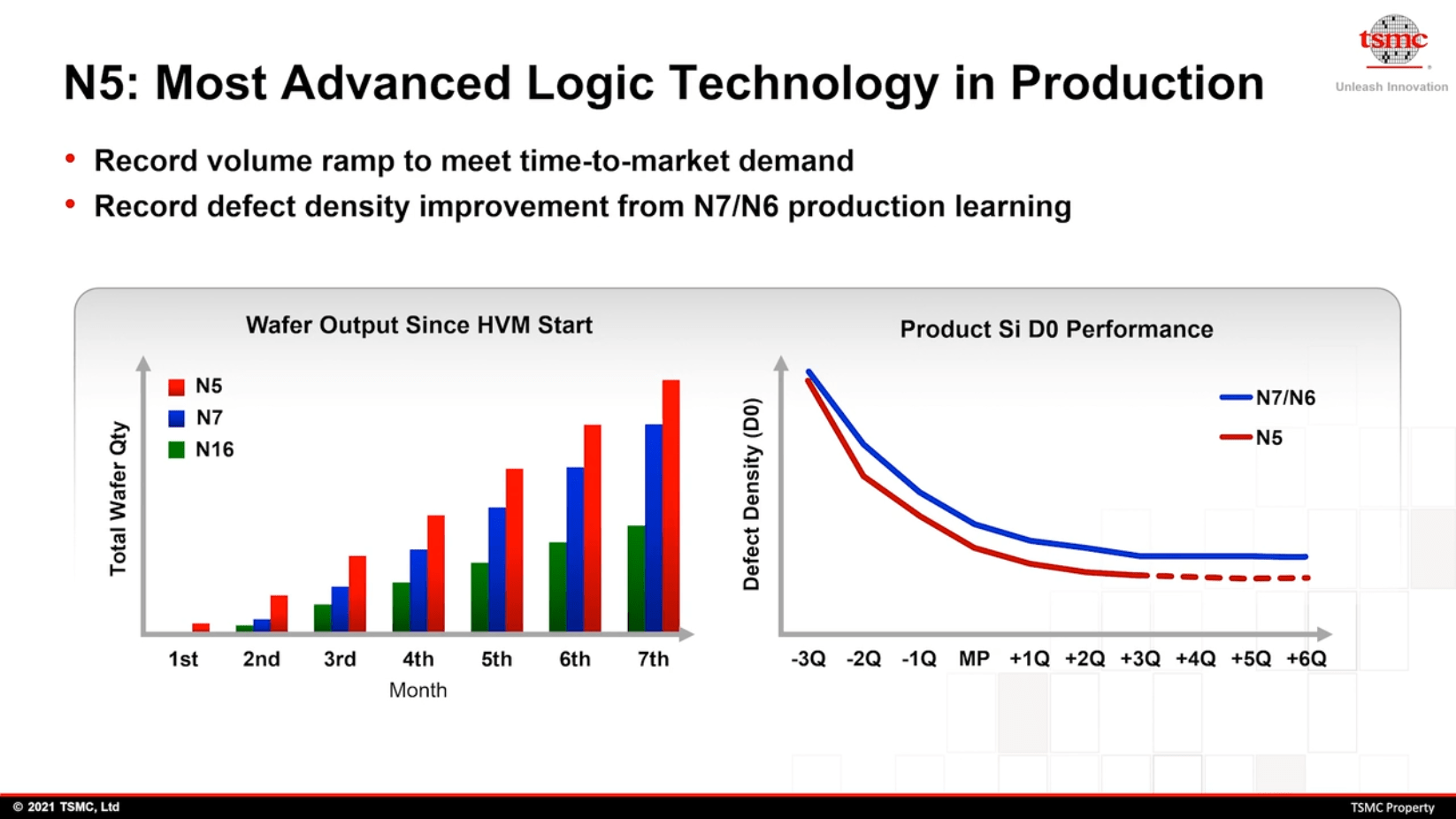

Der N5-Fertigungsschritt geht erst richtig los

N5 erfreut sich großer Beliebtheit, wenngleich bisher nur wenige Partner in den Genuss der aktuell besten Fertigungsstufe gekommen sind. Über 40 Tape-outs von Produkten sollen in diesem Jahr für 5 nm auf dem Programm stehen, die aus allen Bereichen kommen. Das Smartphone rückt dann weiter in den Hintergrund, vor allem AI, Netzwerktechnik für 5G sowie im HPC-Segment ist N5 gefragt.

Über eine halbe Million Wafer mit 5-nm-Chips hat TSMC bereits ausgeliefert. N5A für das Automotive-Segment soll in Zukunft den Weg für diesen Markt weiter öffnen, wenn er ab Ende 2022 zur Verfügung steht. Genau diesen Fertigungsschritt plant TSMC auch für die neue Fabrik in den USA, die mit N5 in drei Jahren starten wird. Einmal mehr ein Hinweis, dass TSMCs Fabrik in den USA zwar sehr modern, aber eben nicht das Allerbeste zu Beginn aufbieten wird.

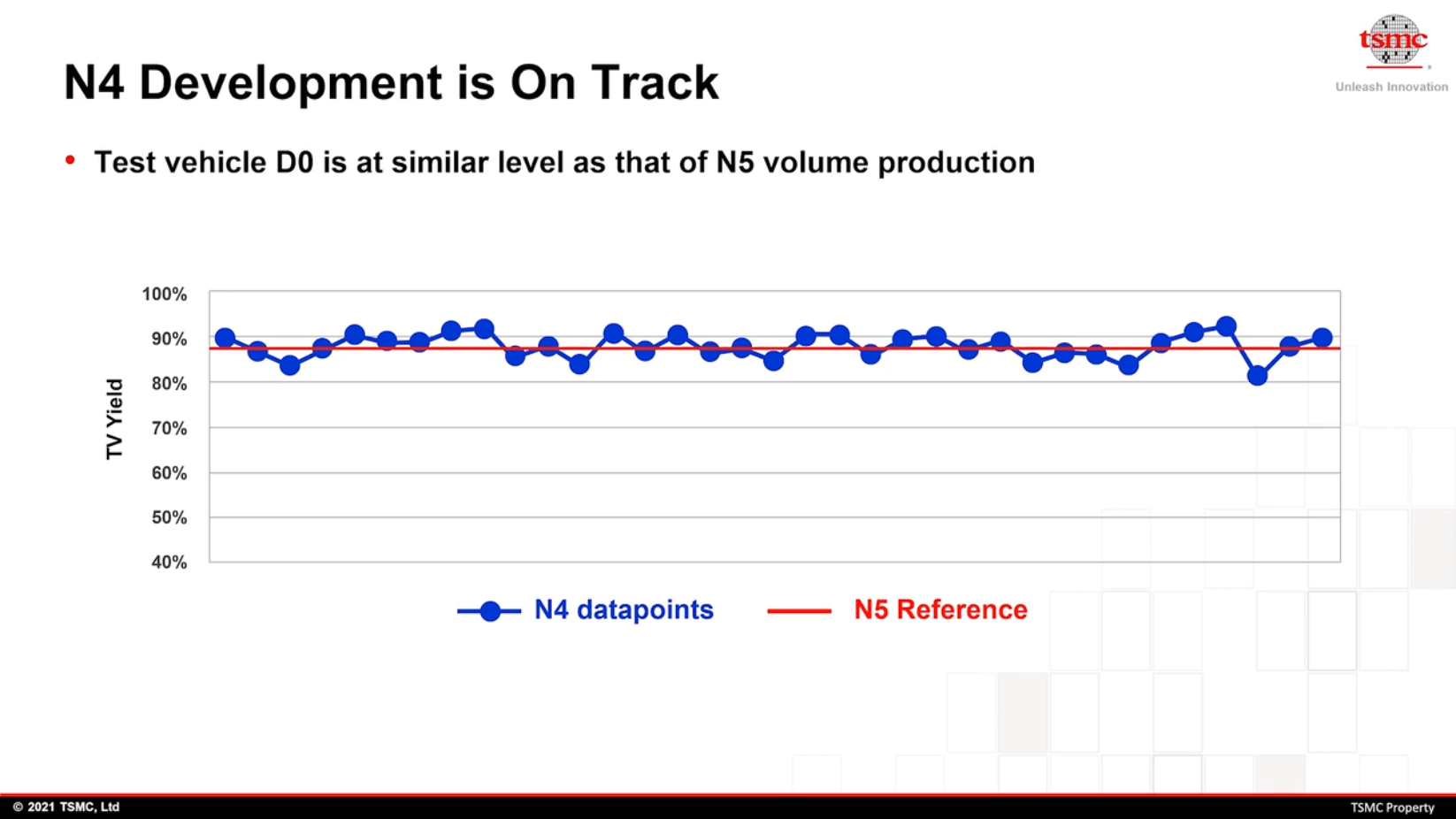

N4 wird der nächste Schritt für die Masse

N4 setzt bei N5 an und fällt durch einen Shrink sechs Prozent kleiner aus. Da der Großteil der Technik von N5 übernommen wird, ähnelt N4 im Vergleich zu N5 dem, was N6 jetzt zu N7 ist. Vor allem für den Mainstream-Markt wird dieser Node in einigen Jahren eine wichtige Option sein, während das Premium-Segment schnell zu N3 wechseln wird.

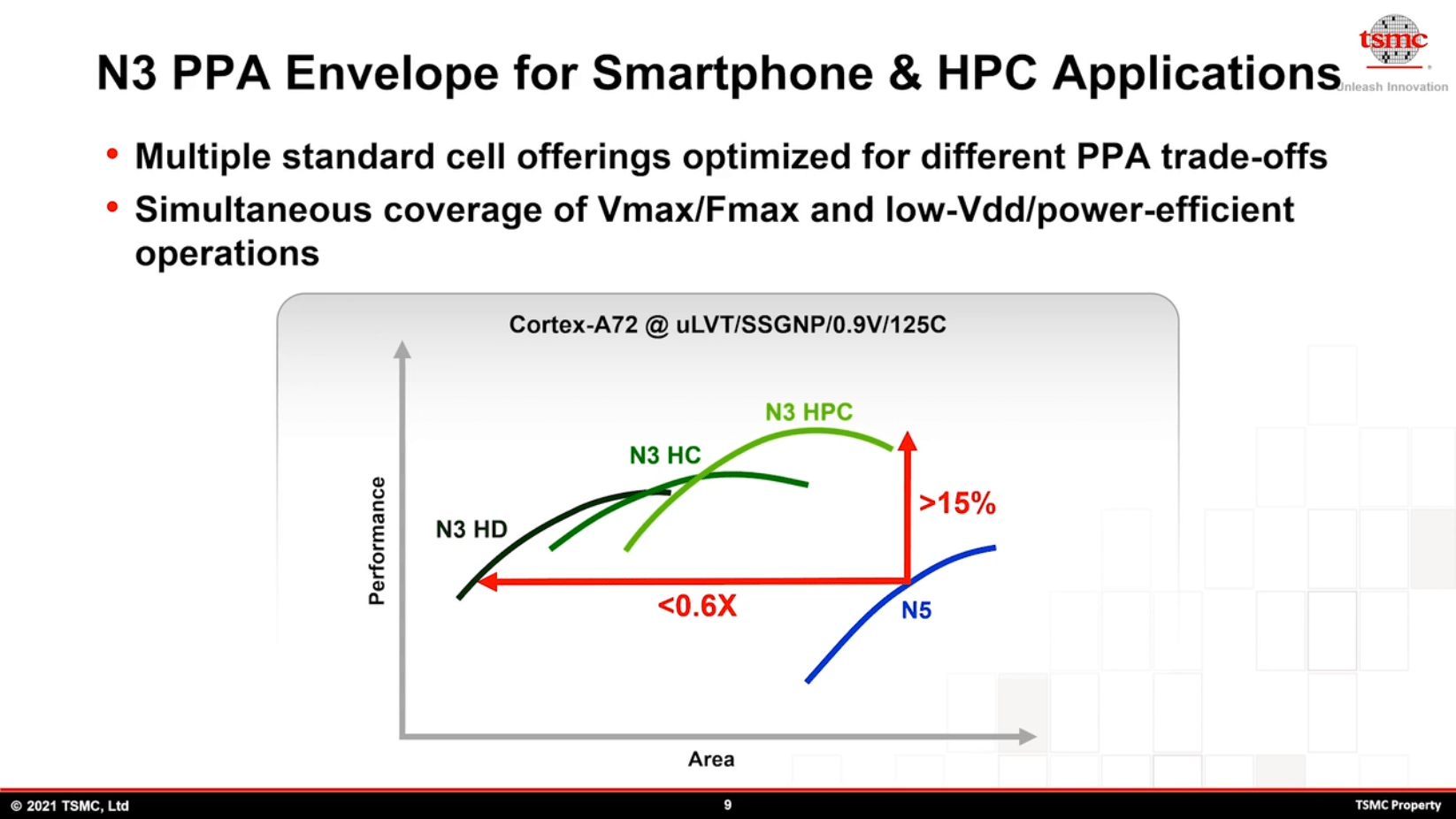

N3 als Premium-Lösung Ende 2022

Zum N3-Prozess mit Massenproduktion im zweiten Halbjahr des kommenden Jahres gab TSMC das bereits Bekannte zu Protokoll. Noch einmal auf klassische FinFETs setzend soll es je nach Einsatzgebiet 15 Prozent schneller sein oder 30 Prozent weniger Leistung aufnehmen, in jedem Fall wird die Dichte weiter deutlich erhöht. Gegenüber N5 sind die Vorzüge deutlich, so wie es sich für ein sogenanntes „Full-node scaling“ gehört. Gegenüber N5 hat der neue Schritt N3 bereits mehr als doppelt so viele Tape-outs von Kunden erhalten, was für die zukünftige Fertigung spricht.

Nach 3 nm: Optimismus

In die Karten lässt sich TSMC für die Zukunft nur ungern schauen und spricht deshalb defacto über N2 noch gar nicht. Die Forscher arbeiten an vielen Dingen, die typischen sind dabei wie seit Jahren schon Nanosheets und Nanotubes. Man merkt den Aussagen des Unternehmens dabei an, dass sie, wie der CEO höchstpersönlich betonte, der zuverlässige Partner sein wollen, stetige Kadenz ist also gefragt. Insofern dürfte ein sehr auf Sicherheit geprägter Fertigungsschritt anstehen, TSMC wird nichts über den Zaun brechen oder übermütig werden, so wie Intel seinerzeit bei 10 nm. Das war letztlich auch für TSMC ein gutes Lehrbeispiel. Auf die Roadmaps schreibt TSMC deshalb N2 heute lieber noch nicht, erst im kommenden Jahr will das Unternehmen darüber reden.