Wie kommst du drauf? Hast du eine Quelle dafür, dass ein solcher geplant ist?pipip schrieb:nebulein

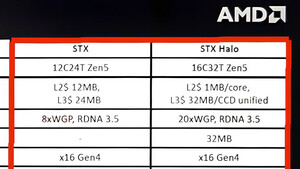

Mit was man rechnen darf ist ein l3 cache beim Kaveri

IMHO steht das in völligem Widerspruch zum HSA Konzept und gemeinsame Speicherbereiche für GPU und CPU. Ein weiterer Cache Level würde nur die Latenzen erhöhen und den Vorteil zunichte machen den man dadurch erhält, dass man sich das kopieren zwischen CPU und GPU Speicherbereichen spart.

Kabini (APU mit Jaguar Kernen) kommt mit einem gemeinsamen L2 Cache für alle Cores. Ich denke es geht viel eher in diese Richtung mit Kaveri und stellt somit deutlich mehr schnellen Cache für Singlethreaded Szenarien zur Verfügung, wo der L3 eben auch die grössten Vorteile bringt. Integration und gemeinsam genutzte ressourcen sind der Weg den AMD geht. Hier passt weder zusätzlicher L3 Cache rein noch stacked Memory für APUs.

Zuletzt bearbeitet:

(Keveri->Kaveri)