Skylake-EP: 28-Kerne-Server-CPUs zeigen geänderte Cache-Größen

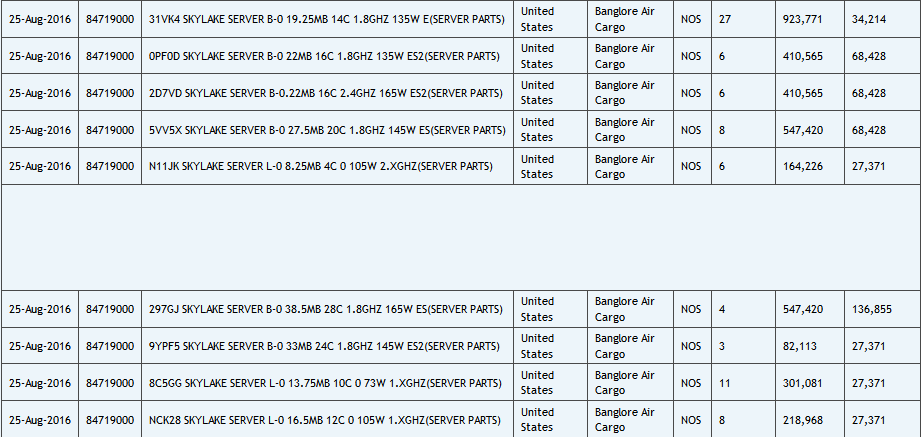

Indiens Import-Datenbank Zauba ist einmal mehr für Details zu anstehenden Produkten gut. Heute sind es die kommenden Xeon E5 v5 alias Skylake-EP, die in verschiedenen Größen bis zum Vollausbau mit 28 Kernen und 56 Threads verschickt wurden. Die Einträge bestätigen darüber hinaus Anpassungen beim L3-Cache.

Laut den Einträgen liegen die aktuellen Samples, die je nach Modell mit 1,8 bis 2,4 GHz takten, bereits im B0-Stepping vor und haben damit schon erste Optimierungen und Fehlerbehebungen erfahren. Im Frühjahr wurde noch das A2-Stepping getestet. Zudem zeigen die Einträge auch ein zweites Stepping L0 an, was darauf hindeutet, dass Intel mindestens wieder zwei Die-Größen auflegen wird. Denn L0 ist laut den Einträgen nur bei den Skylake-EP-Prozessoren mit vier bis maximal zwölf Kernen zu finden, B0 hingegen reicht von 14 bis 28 Kernen.

Deutlich weniger L3-Cache als bisher

Die interessanteste Neuerung ist nicht der Sprung auf 28 Kerne und 56 Threads von aktuell derer bereits 24 und 48 bei Broadwell-EP/EX, sondern die Cache-Größe. Dort bestätigt die Datenbank als Maximalausbau 38,5 MByte für 28 Kerne, was in nur noch 1,375 MByte pro Kern resultiert – exakt dieser Wert tauchte vor einigen Wochen bei Skylake-X für den Desktop-Einsatz das erste Mal auf. Dort wurden 13,75 MByte L3-Cache für maximal zehn Kerne genannt.

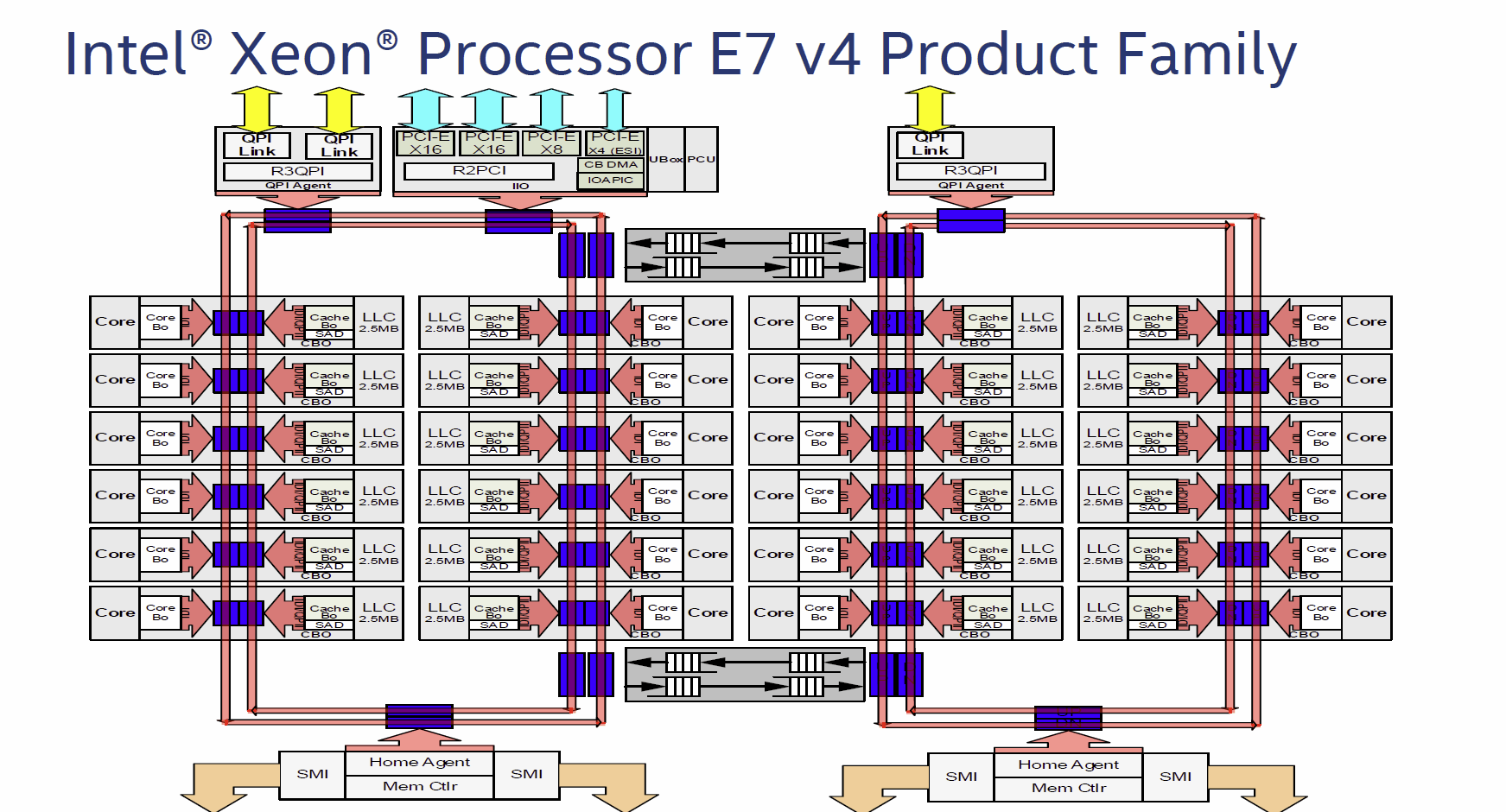

Im absoluten High-End-Bereich wäre dies auf dem Papier ein drastischer Rückschritt: Der Xeon E7-8890 v4 bietet heute mit 24 Kernen und 48 Threads 60 MByte L3-Cache. Intel dürfte auf Seiten der Architektur und des Die-Aufbaus aber diverse Dinge verändert haben, um die fehlende Menge beispielsweise durch höhere Geschwindigkeiten und direktere Zugriffe wieder wett zu machen. Denn der aktuelle Broadwell-EP/EX ist hinsichtlich der Kommunikation zwischen Kernen und Cache bereits eine kuriose Lösung: Er besitzt zwei doppelte Ringe, die über zwei Buffer miteinander kommunizieren. Dadurch gibt es in gewissen Einsatzszenarien mitunter einen Flaschenhals. Wie genau Intel das bei Skylake-EP gelöst hat, ist noch unbekannt.

Testsamples mit 4 bis 28 Kernen

Im Umlauf sind laut Datenbank diverse Modelle mit lediglich vier Kernen und größeren L3-Caches für Spezialmodelle und die Flaggschiffe mit 24 und bis 28 Kernen bei TDP-Spannen von 73 bis 165 Watt. Die Obergrenze ist damit eine Altbekannte, auch heute kommt der Maximalausbau stets mit 165 Watt in den Handel. Mit einem Marktstart von Skylake-EP wird frühestens im kommenden Sommer gerechnet, wahrscheinlicher ist das zweite Halbjahr, in dem die Purley-Plattform debütieren wird.