Intel vs. AMD: Intel stichelt weiter gegen „zusammengeklebte Dies“

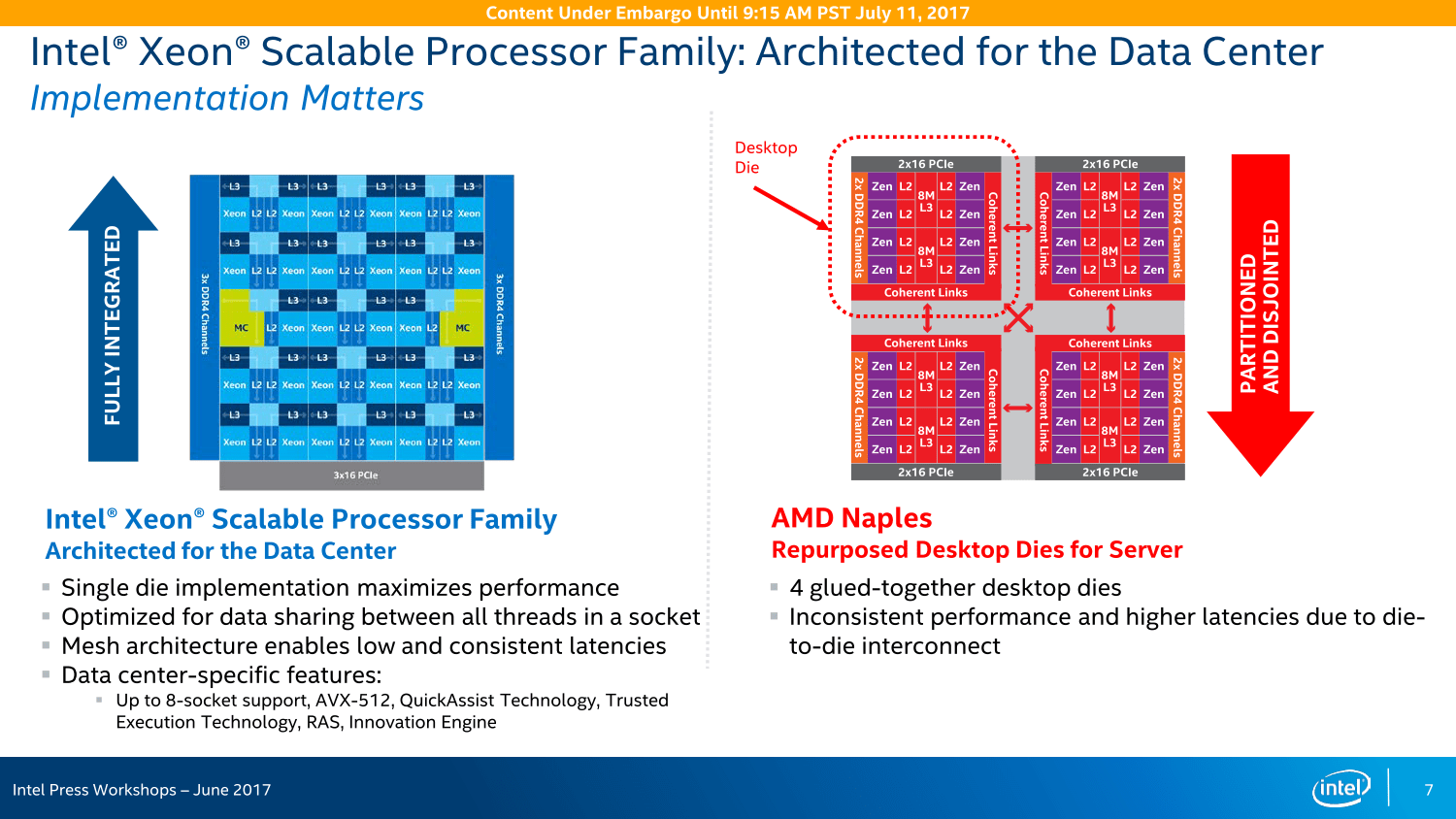

Auch etwas über einem Jahr nach den ersten Epyc- und Threadripper-Prozessoren von AMD mit einem Multi-Chip-Package aus bis zu vier einzelnen CPU-Dies stichelt Intel weiterhin gegen diese Lösung. So hat im Juni 2017 diese PR-Geschichte angefangen.

In einem neuen Posting erklärt einer von Intels führenden Architekten, dass sie auch in Zukunft den Ansatz des nativen monolithischen Dies verfolgen werden. Zumindest in naher Zukunft, denn Skylake-SP wird aus dem Server-Segment mit 28 Kernen einfach in den Desktop portiert. Gleichzeitig wird die Alternative von AMD mit der Phrase „patching together“ in kein gutes Licht gerückt, denn dieser Ausdruck steht im Englischen für eine schnelle aber nicht wirklich gute Lösung. Umgangssprachlich übersetzen ließe sich der Ausdruck als „zusammenflicken“.

Our approach to deliver high core counts is to use monolithic dies instead of patching together a group of small dies.

Intel

Mit sehr ähnlichen Worten hatte Intel im Juni 2017 den Feldzug gegen AMDs damals noch nicht einmal offiziell vorgestellte Server-Plattform Epyc, Codename Naples, gestartet. Seinerzeit wurden die Lösungen sogar noch als „glued-together desktop dies“ bezeichnet, also zusammengeklebte Dies eines Desktop-Prozessors.

Dass sich diese Lösungen mittlerweile mitunter als sehr konkurrenzfähig erwiesen haben, hat aber auch Intel registriert. Durch das Mehr an Kernen und der Speicheradressierung gibt es Einsatzszenarien, in denen Intels Xeon nicht mithalten kann. Dieser wiederum punktet über die höhere IPC, zum Teil geringere Latenzen und Zusatzinstruktionen wie AVX-512. Aber auch in den Bereichen, in denen mehr als zwei CPU-Sockel zum Einsatz kommen, ist Intel Platzhirsch, wie die kürzlich veröffentlichte Rekord-Liste von Intel offenbart. Dort wirbt der Hersteller mit 95 Weltrekorden für Xeon-SP, viele davon entfallen aber auf Drei-, Vier-, Sechs- und Acht-Sockel-Systeme, die AMD gar nicht adressiert. Epyc ist auf maximal zwei Sockel beschränkt, auf die wiederum zusammen mit dem Single-Sockel der Großteil des Marktes entfällt.

Multi-Chip-Module auch in Zukunft

Dass Intel in Zukunft auch im CPU-Bereich auf Multi-Chip-Lösungen verzichtet, ist indes fraglich. Die Vergangenheit bestand auch bei Intel bei den ersten Zwei- und Vier-Kern-CPUs aus nichts anderem als zwei „zusammengeleimten“ Chips auf einem Package, mit EMIB hat der Hersteller nun zudem eine neue Technik im Programm, die dafür geradezu prädestiniert ist. Zwischenzeitlich hatte Intels Webseite bereits einen CLX-AP gelistet, der 5.903 Kontaktflächen besitzt. Cascade Lake-AP soll vermutlich zwei Prozessor-Dies oder ein CPU-Die kombiniert mit FPGA oder RAM auf einem EMIB-Package hervorbringen.