IDF: Quad-Core in FPGAs aus Braunschweig

Die Entwicklung eines komplexen, mehrere 100 Millionen Transistoren umfassenden Prozessors ist kompliziert und zeitaufwendig. Insbesondere in der Anfangsphase der Entwicklung – es ist nicht einmal an ein in Silizium gegossenes Engineering Sample zu denken – wird in der Industrie sehr häufig mit FPGAs gearbeitet.

Die Abkürzung FPGA steht für „Field Programmable Gate Array“ und beschreibt eine durch Software programmierte Hardware-Logik. Mit ihr können beliebige Hardware-Funktionen realisiert werden. Dies ermöglicht Entwicklern sogenanntes Rapid Prototyping, in dem Ideen schnell ausprobiert und umgesetzt werden können, ohne auf reales Silizium angewiesen zu sein, für dessen Produktion von der Wafer-Maske bis hin zum im Package untergebrachten Chip Monate vergehen können. Monate in den neben der Hardware- auch die Software-Entwicklung kaum Fortschritte machen kann.

Dementsprechend beliebt sind FPGAs unter Hardware-Entwicklern, auch wenn die zum Programmieren der FPGAs benötigten Software-Umgebungen ihre Eigenheiten haben. Auch Intel setzt zur Forschung an ihren Tera-Scale-Projekt mit dem (noch) fernen Ziel von hunderten von Prozessorkernen auf einen Chip mit einer Leistung von über 1 Billion Instruktionen pro Sekunde (Tera-Instuctions, seien es FLOPS oder IPS) FPGAs ein. Die Herausforderung bei einem Prozessor mit über 100 Kernen besteht unter anderem darin – neben dem Erreichen entsprechender Transistordichten, so dass entsprechend große Kerne kosteneffizient gefertigt werden können – die Kommunikation der Kerne untereinander und der Außenwelt sicherzustellen.

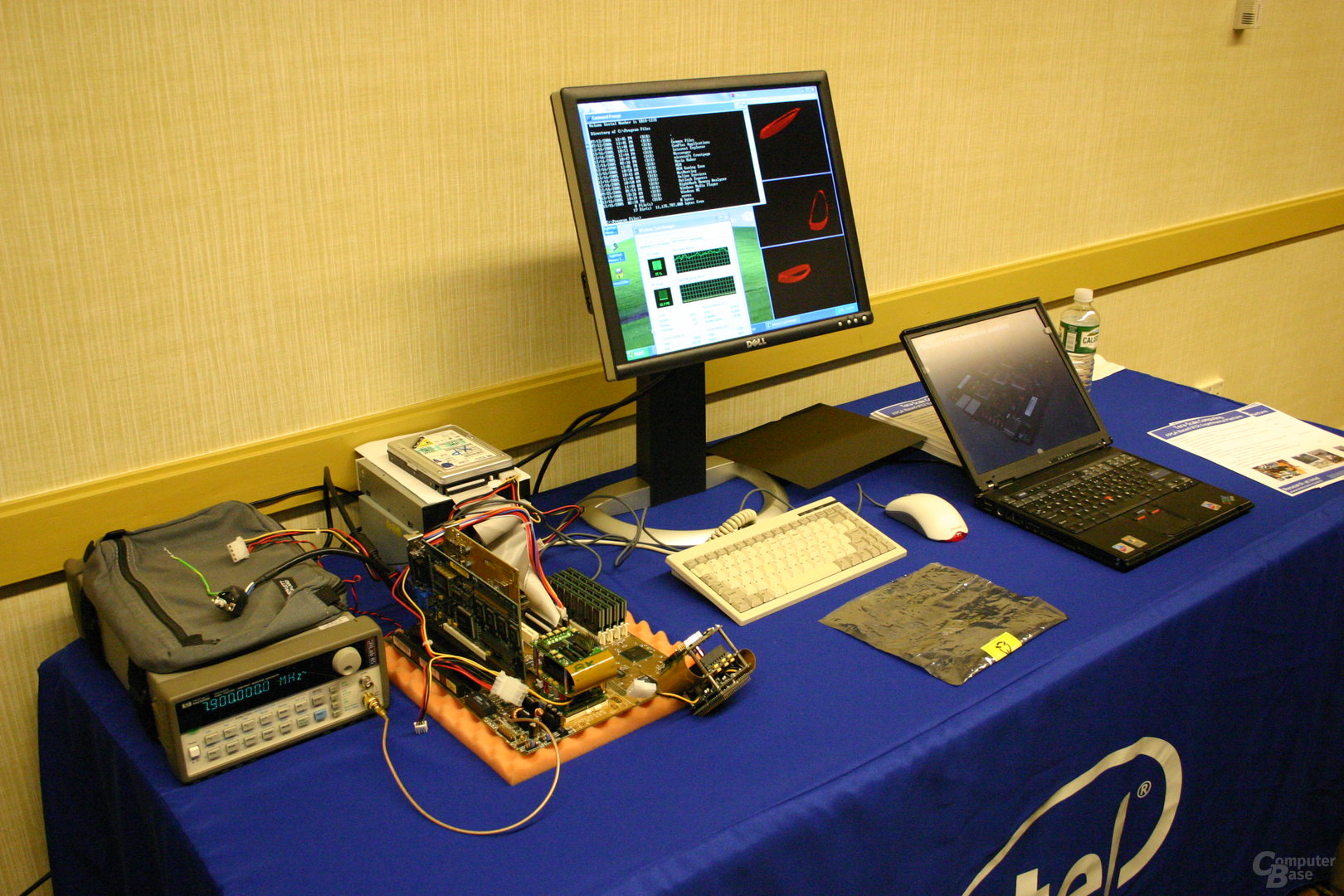

Hierfür stehen verschiedene Konzepte bereit – Daten-Ring oder Mesh-Strukturen. Auch in Braunschweig erfolgt ein Teil der Tera-Scale-Grundlagenforschung. Eine Forschungsgruppe wurde hierfür im April 2006 gebildet. Zur Eröffnung demonstrierte man ein Dual-Core-Prozessor der Pentium-Klasse mit MMX und 5-stufiger-In-Order-Pipe-Line, die in einem Xilinx Virtex 4 FPGA einprogrammiert wurden. Als Testplatine diente dabei das Asus P55T2P4 mit Sockel 7 und 430HX-Chipsatz. Auch auf dem IDF Fall 2006 in San Francisco ist dieses System – allerdings nur in einer Single-Core-Ausführung – vertreten.

Der in den FPGA von Xilinx einprogrammierte x86-Prozessor nutzt in etwa 40 Prozent des Virtex 4 und wurde mit 30 MHz getaktet. Der Taktgeber des Mainboards wurde dabei von außen mit einer Referenzschwingung von 1,9 MHz umgangen. Trotz des niedrigeren Prozessortakts von nur 30 MHz war das System in der Lage Windows XP zu booten.

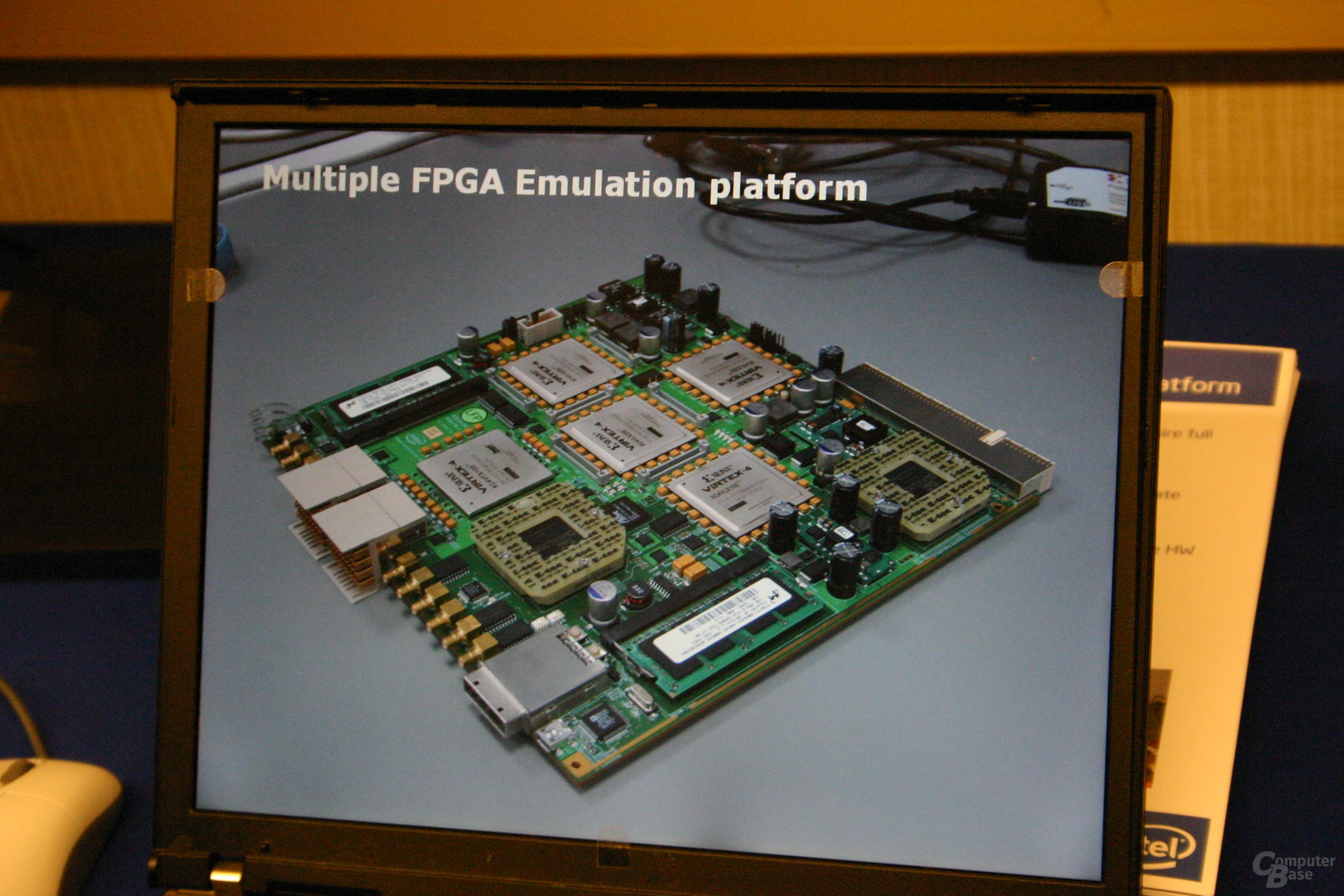

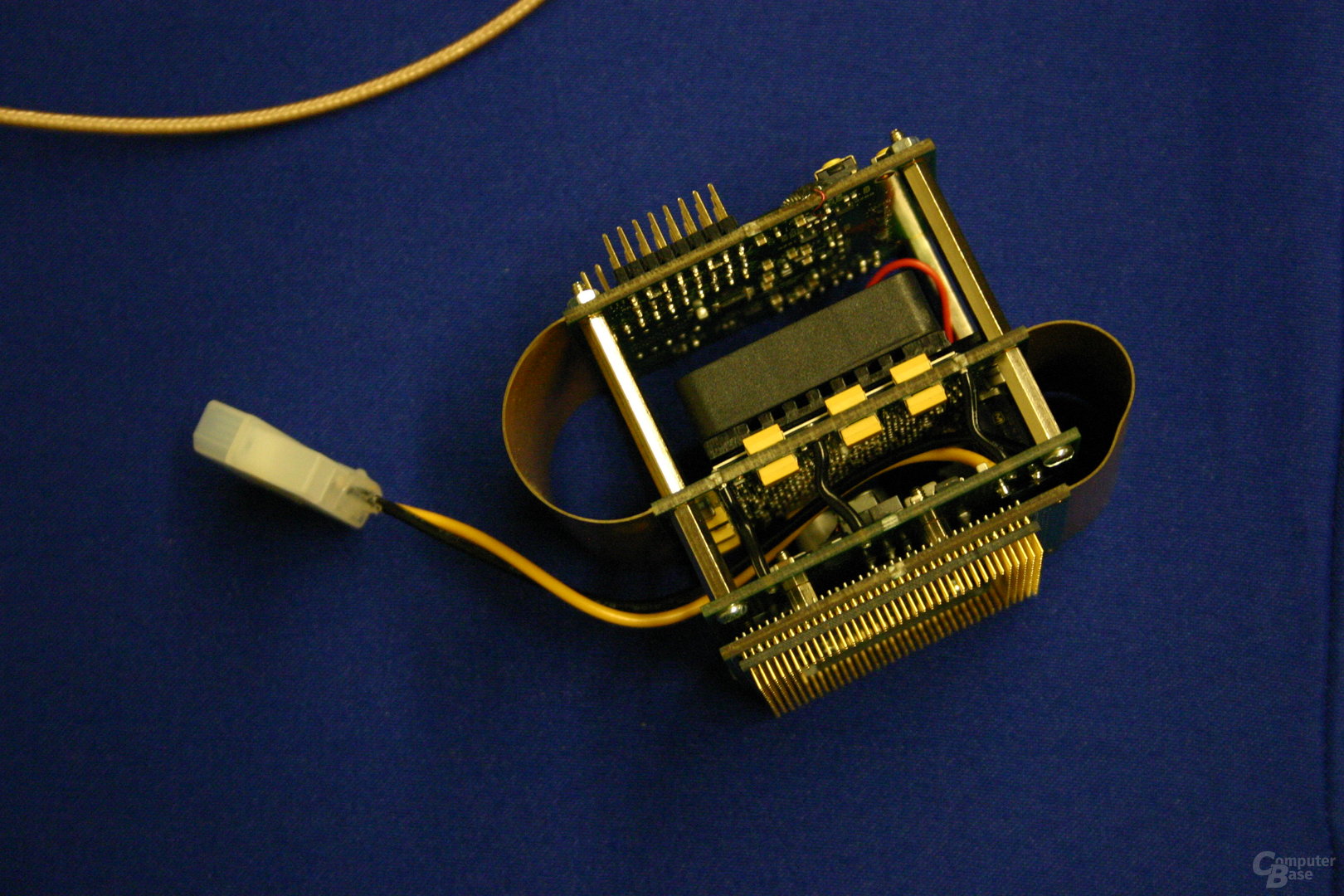

Während Intel auf dem IDF nur einen, mittels FPGA realisierten Single-Core-Prozessor zeigt, wurden die Entwickler in Braunschweig inzwischen mit neuer Hardware ausgerüstet. Nun darf an Platinen mit insgesamt vier FPGAs entwickelt werden. Darüber hinaus stehen nun Steckverbindungen (weißer Stecker, siehe Fotos) zur Verfügung, um mehrere Platinen miteinander zu verbinden und damit Experimente mit „Many“-Cores durchzuführen.