High Bandwidth Memory: Samsung stapelt 12 Layer DRAM für 24-GB-Bausteine

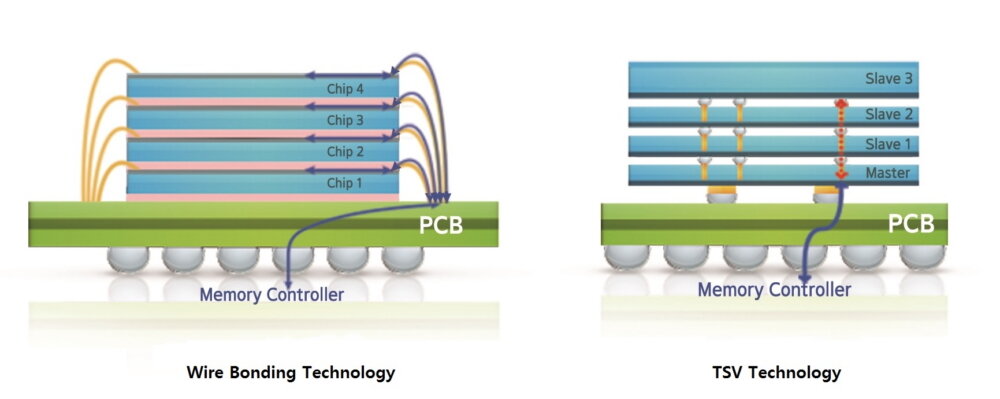

Samsung hat seine Technik für Stacked DRAM mit Silizium-Durchkontaktierung (TSV) weiter verfeinert und stapelt nun zwölf statt bisher acht Schichten (Layer) übereinander, ohne dass das Chipgehäuse dicker wird. Damit soll die Speicherkapazität von High Bandwidth Memory (HBM) auf 24 GB pro Stapel steigen.

12 gestapelte DRAM-Chips für 24 GB HBM2

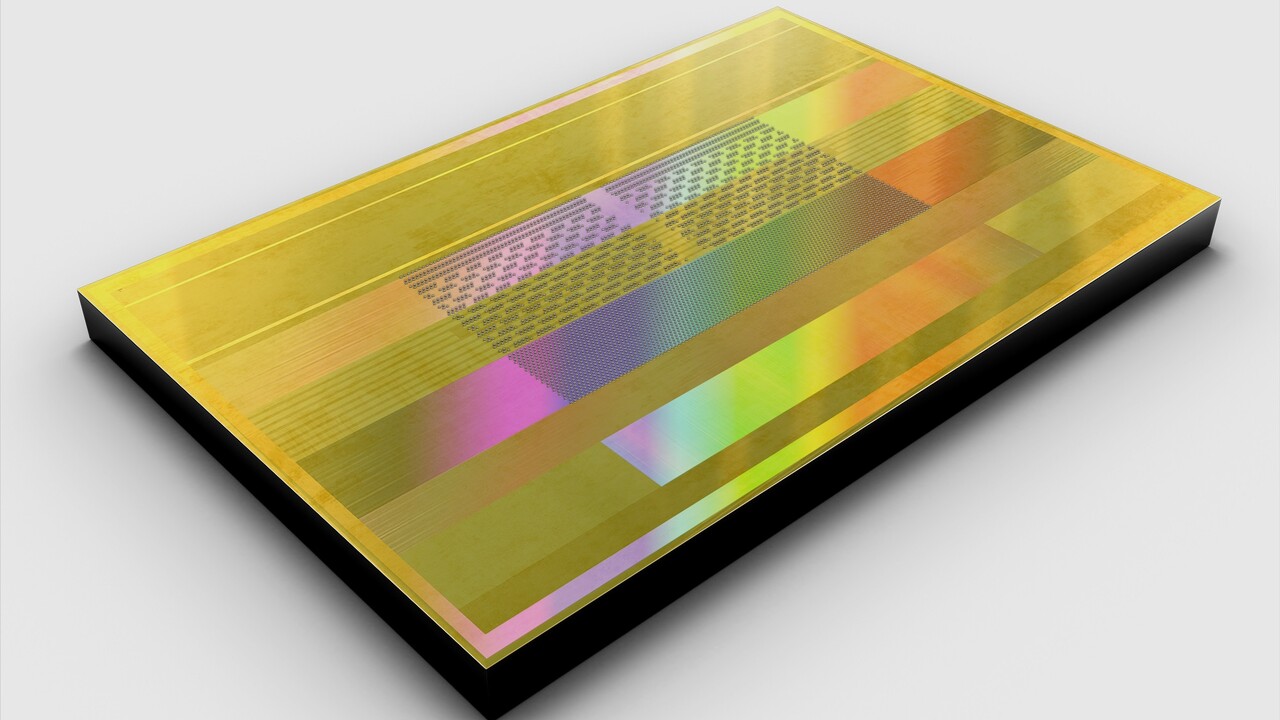

Samsung spricht von der ersten „12-layer 3D-TSV (Through Silicon Via) technology“ der Branche, bei der angeblich mehr als 60.000 der sogenannten TSV Holes als vertikale elektrische Verbindung der zwölf DRAM-Chips dienen. Kombiniert mit DRAM-Chips der jungen 16-Gigabit-Generation, bedeutet dies zwölf Mal 2 Gigabyte Speicherkapazität in einem Chip-Gehäuse (Package). Künftiger High Bandwidth Memory soll somit 24 GB pro Package besitzen. Derzeit ist noch HBM mit acht gestapelten 8-Gigabit-Chips üblich, der entsprechend nur 8 GB erreicht. HBM wird vor allem bei High-End-Grafikkarten und Netzwerkgeräten eingesetzt und neben Samsung auch von SK Hynix hergestellt.

Package nicht dicker als bisher

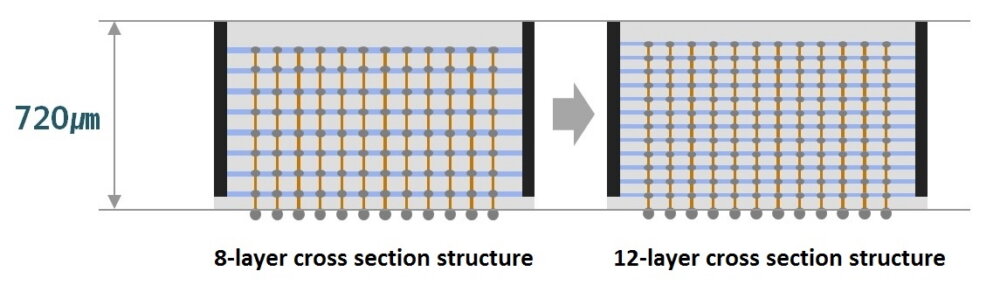

Laut Samsung fällt ein 12-Layer-DRAM-Package mit 720 µm Dicke nicht höher aus als ein HBM2-Package mit acht Ebenen. Entsprechend sind diesbezüglich keine Änderungen an den Produktdesigns der Kunden nötig. Eine Abbildung deutet sowohl dünnere Speicherchips als auch geringere Abstände zwischen diesen an, ist aber vor allem symbolisch zu verstehen. Einen genauen Termin für den „baldigen“ Start der Massenproduktion hat Samsung noch nicht genannt.

JEDEC hat 12 Layer bereits abgesegnet

Von Seiten des Speichergremiums JEDEC besteht schon lange grünes Licht für HBM mit 12 DRAM-Schichten und 24 GB pro Package. Bereits im Dezember 2018 wurden die Spezifikationen für HBM2 in Form der Version JESD235B entsprechend aktualisiert. Teil des neuen Standards ist auch eine höhere Datenrate von 2,4 Gbit/s pro Pin, was beim immer noch 1.024 Bit breiten Speicherinterface einen Durchsatz von 307 GB/s bedeutet. Durch Kombination mehrerer HBM-Stapel erreichen High-End-Grafikkarten einen Speicherdurchsatz von 1 Terabyte pro Sekunde.

HBM2E mit deutlich mehr Durchsatz

Mit dem im kommenden Jahr erwarteten HBM2E soll die Datenrate pro Pin auf bis zu 3,6 Gbit/s steigen und der Speicherdurchsatz pro Package auf 460 GB/s anwachsen. HBM3 und HBM4 sollen die Datenrate in den kommenden Jahren weiter steigern.