AMD-Epyc-Roadmap: Genoa-X, Siena als Low-Cost-64C-CPU, Turin mit Zen 5

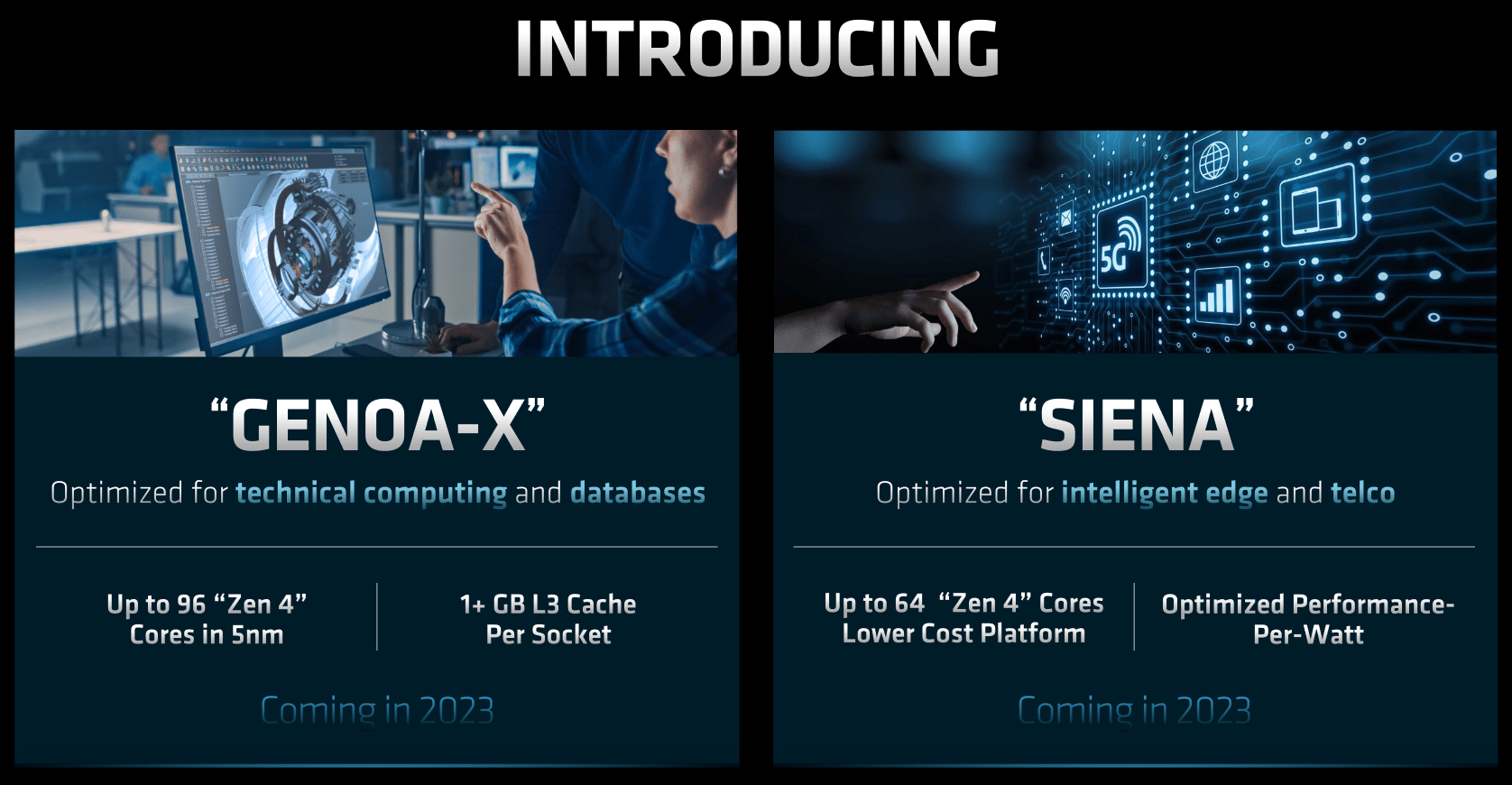

Die Server-CPU-Roadmap von AMD ist mittlerweile allumfassend und diversifiziert wie nie zuvor. Für Zen 4 gibt es 4 Versionen, von der normalen Variante in Form von AMD Genoa über Genoa-X mit 3D-V-Cache bis zu AMD Bergamo mit kleinen Zen-4c-Kernen. Neu hinzu kommt ein Low-Cost-Ableger.

Siena bietet im Sockel SP6 den neuen Einstieg

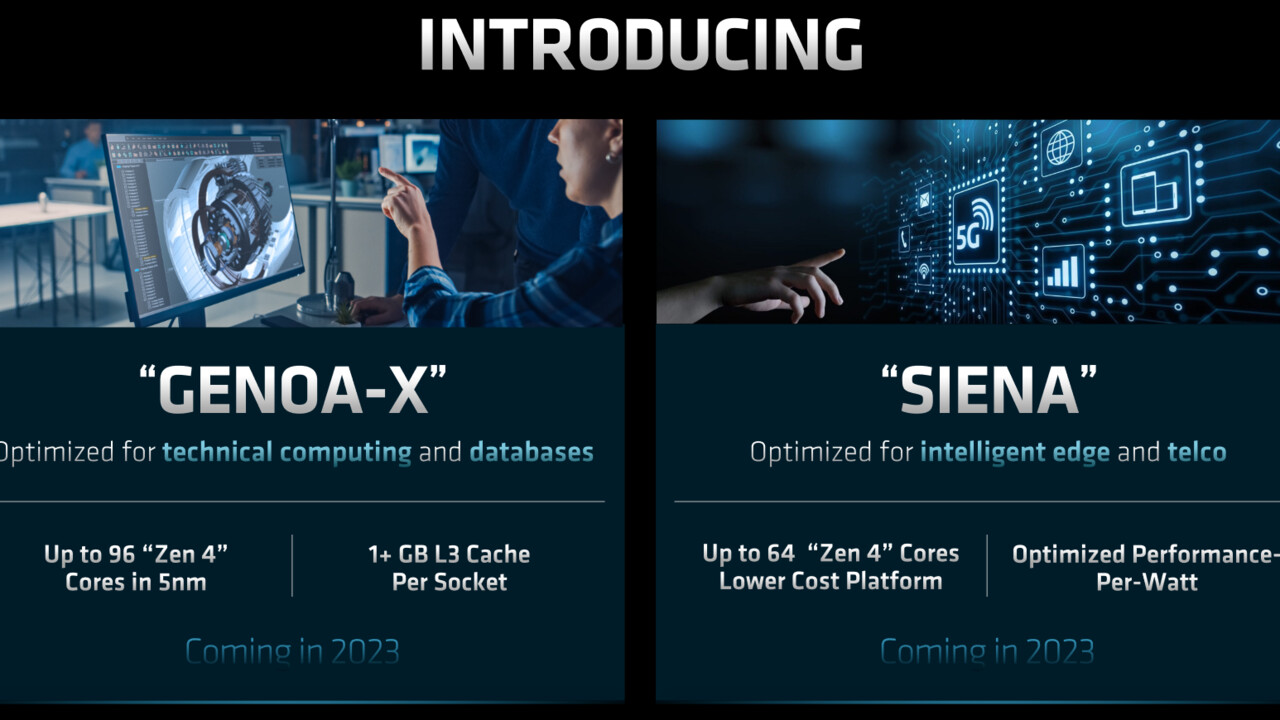

„Siena“ tauft AMD diese neue Lösung und sie passt exakt zu dem, was zuletzt bereits durch erste Spezifikationen nicht der CPU selbst, sondern des kleineren Sockels SP6 bekannt wurden. Mit dem Wissen lässt sich Siena schon deutlich besser einordnen, wenngleich AMD diese Details heute noch nicht bestätigt hat, schließlich erfolgt der Marktstart erst im kommenden Jahr 2023.

Ein kleinerer Sockel, halbiertes Speicherinterface und die zumindest offiziell bestätigte Kürzung der Kerne auf 64 Stück als Maximum passen zu AMDs Ankündigung, eine „Lower Cost Platform“ aufzustellen, um die Märkte zu bedienen, die keinen teuren und vielleicht sogar übergroßen Genoa auf Sockel SP5 mit 12-Kanal-Speicher benötigen. Dennoch soll Siena nicht so etwas wie Intels Xeon D sein, sondern auf vollwertige Zen-4-Kerne vertrauen, liegt leistungstechnisch also deutlich darüber und wäre so auf dem Papier ein ziemlich guter Kandidat für einen HEDT-Threadripper. Was genau AMD mit diesen vorhat, blieb zum großen Teil im Dunkeln, bestätigt wurde lediglich eine Threadripper-Neuauflage für die Ryzen-7000-Serie.

Genoa-X bietet mit mehr CPU-Dies auch mehr gestapelten L3-Cache

Denn neben Genoa, welche noch im vierten Quartal dieses Jahres vorgestellt werden sollen, wie AMD in der Nacht erklärte, wird Genoa-X als Version mit 3D-V-Cache erscheinen. Nach dem starken Auftritt von Milan-X war dieser Schritt mehr als erwartet worden, erste Details zeigen, dass AMD hier dann „1+ GB L3 Cache“ pro Sockel bieten wird. 1 GByte würde bei 96 Kernen schon bei Nutzung des gleichen Cache-Slices erreicht werden, der bei Milan-X genutzt wird (natürlich angepasst auf den neuen Die). Dort sitzen jeweils 64 MByte auf einem 8-Kern-CPU-Die zusätzlich zu den internen 32 MByte L3-Cache, mit 96 Kernen bei weiterhin genutzten 8-Kern-Dies kommt man durch die externe Lösung bereits auf kombinierte 1.152 MByte L3-Cache pro Prozessor.

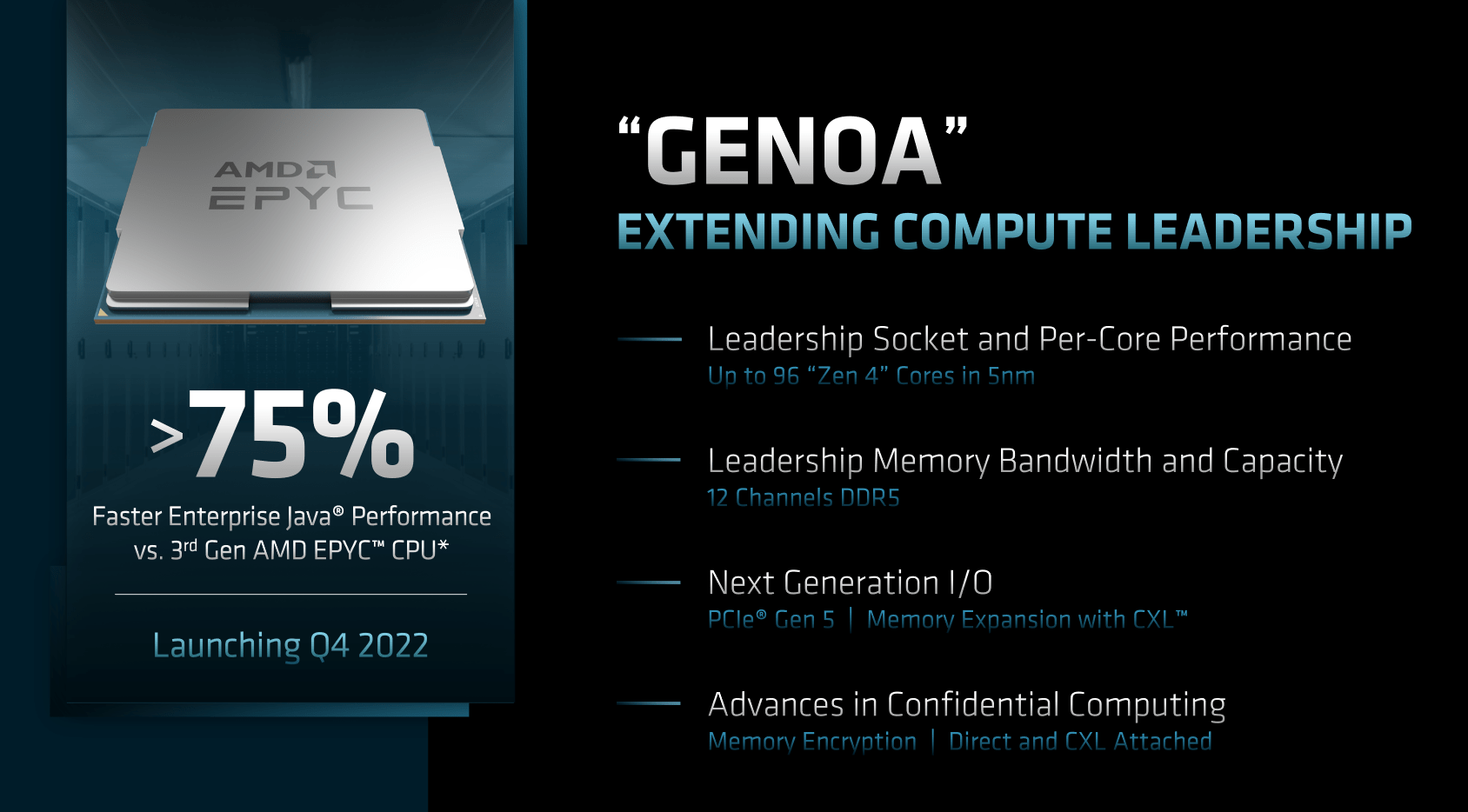

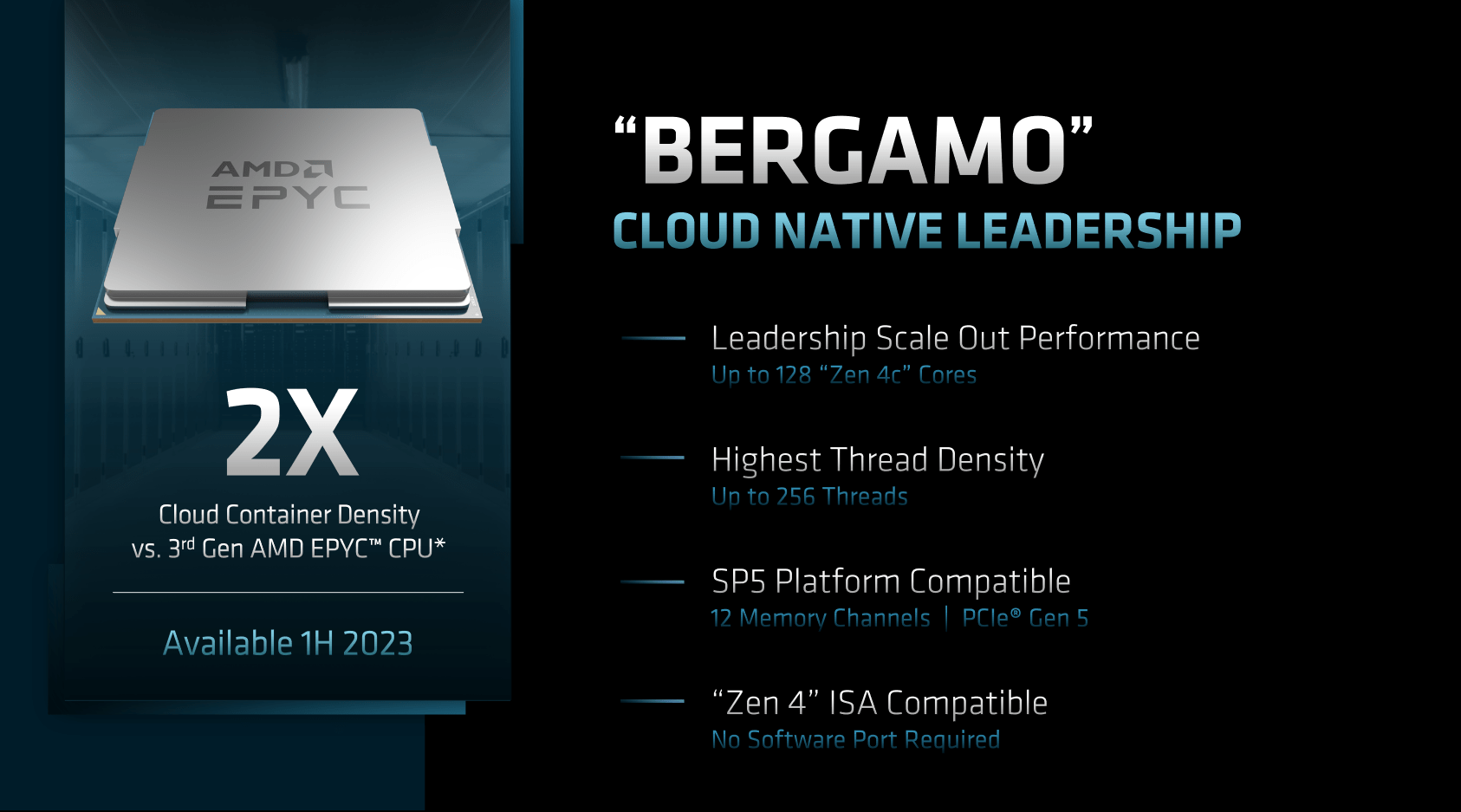

Was vom klassischen AMD Genoa und dem Cloud-Prozessor AMD Bergamo zu erwarten ist, grenzte AMD heute auch noch einmal etwas genauer ein. Das Plus an 50 Prozent mehr Kernen zuzüglich zur um knapp zehn Prozent gesteigerten IPC und dem zusätzlichen Takt soll Genoa zu einer Leistungssteigerung von um die 75 Prozent gegenüber aktuellen Epyc-Prozessoren verhelfen. Rein rechnerisch geht das problemlos auf, das gilt auch für Bergamo: Mit 128 Kernen bietet man hier doppelt so viel wie bisher, der Faktor 2x ist deshalb die logische Folge für gewisse Betrachtungsweisen.

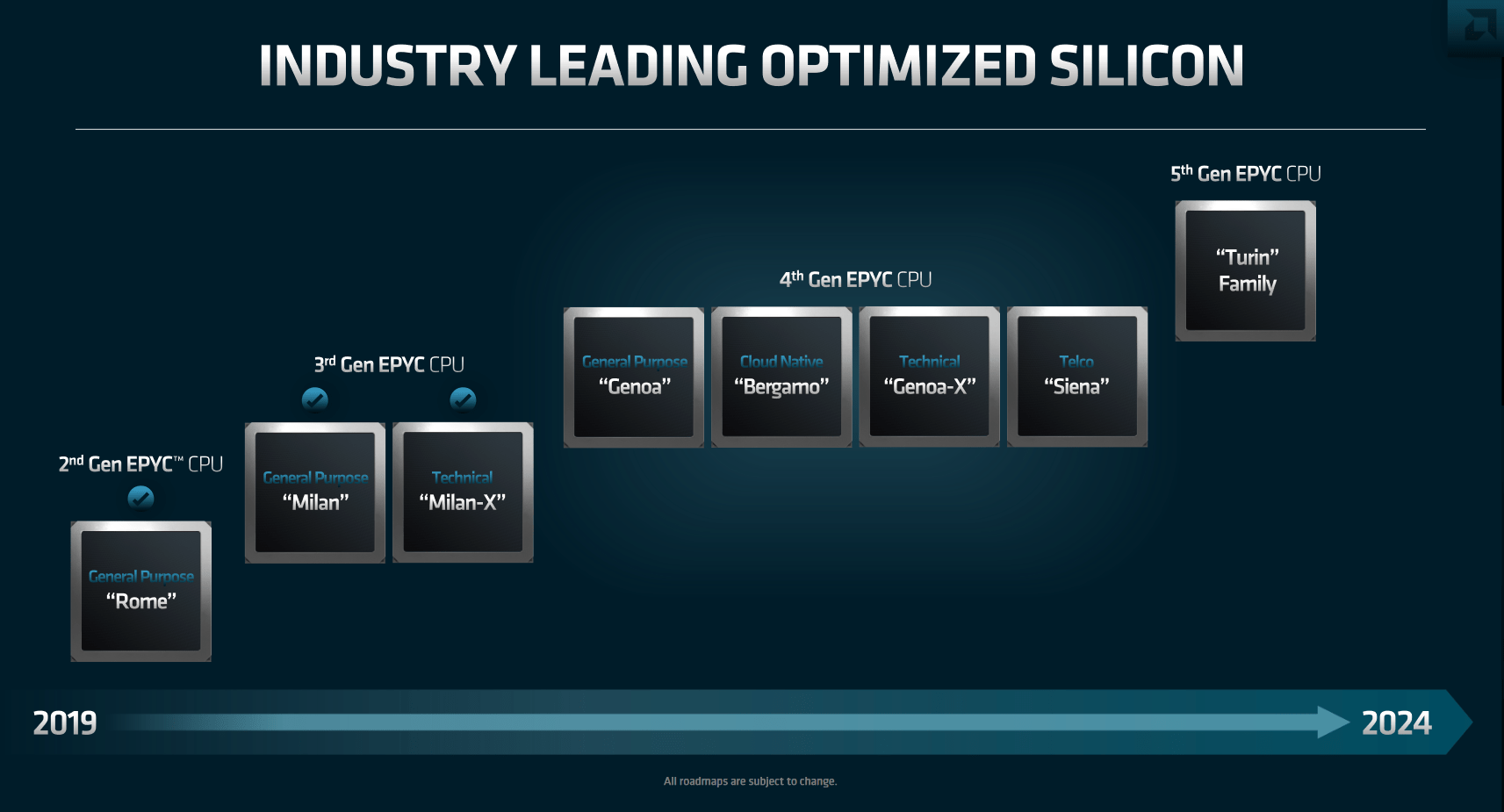

Die AMD-Server-Roadmap bis 2024

In der Roadmap zusammengefasst verdeutlicht AMD noch einmal die Entwicklung. Von einzelnen normalen CPUs wie Naples und Rome begann mit Milan die Diversifizierung und sie wird mit Zen 4 noch einmal einen deutlichen Schritt nach vorn gehen. Auch mit Zen 5 wird das so weiter gehen, auf der Server-Roadmap ist bisher zwar nur Turin vermerkt, aber die Architektur-Roadmap offenbart bereits Zen 5, Zen 5c und Zen 5 mit 3D-V-Cache.