Intel Meteor Lake: Grafikeinheit bekommt L4-Cache, CPU-Teil exklusiv den L3

Neue Linux-Patches beschreiben einen L4-Cache für Intels kommenden Meteor-Lake-Prozessor. Dieser könnte der GPU vorbehalten bleiben, denn einen Zugriff auf den L3-Cache, den die kleine integrierte Grafikeinheit bisher hatte, wird sie laut Eintrag nun nicht mehr haben.

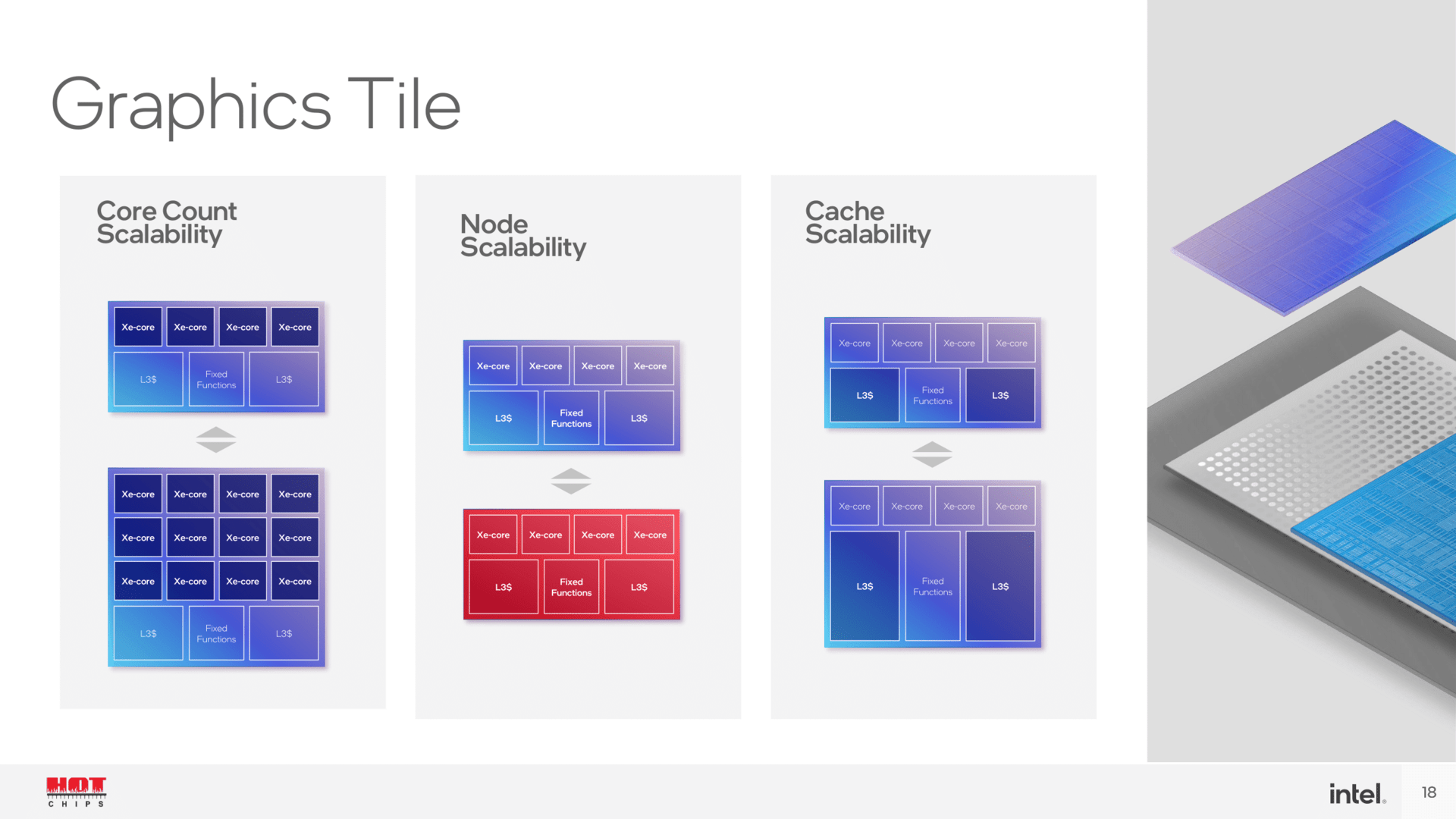

Grafikeinheiten nutzen einen L3-Cache bisher dazu, um primär Zugriffe auf den Grafikspeicher abzufangen. Ein Paradebeispiel dafür ist AMDs GPU-Architektur RDNA 2 und die Einführung des Infinity Caches mit einer Größe von bis zu 128 MByte, der viel Leistung zu vergleichsweise kleinem Preis brachte. Bei Intel gibt es so etwas aktuell nicht. Die kleine integrierte GPU darf zwar auf den L3-Cache im SoC neben der CPU zugreifen, das ist aber natürlich nicht das gleiche wie AMDs Ansatz. Die Einführung einer Cache-Stufe für die Grafikeinheiten im SoC, die wiederum keinen Zugriff mehr auf den L3-Cache (LLC) haben, scheint hier eine möglicherweise angestrebte Lösung zu sein. Da Meteor Lake als Kachel-Chip aufgelegt wird, also einzelne Bausteine auf einem Package vereint werden, wäre auch ein separater On-Package-Cache denkbar – eben so, wie eDRAM seinerzeit.

On MTL, GT can no longer allocate on LLC - only the CPU can.

This, along with addition of support for ADM/L4 cache calls a

MOCS/PAT table update.

Intel

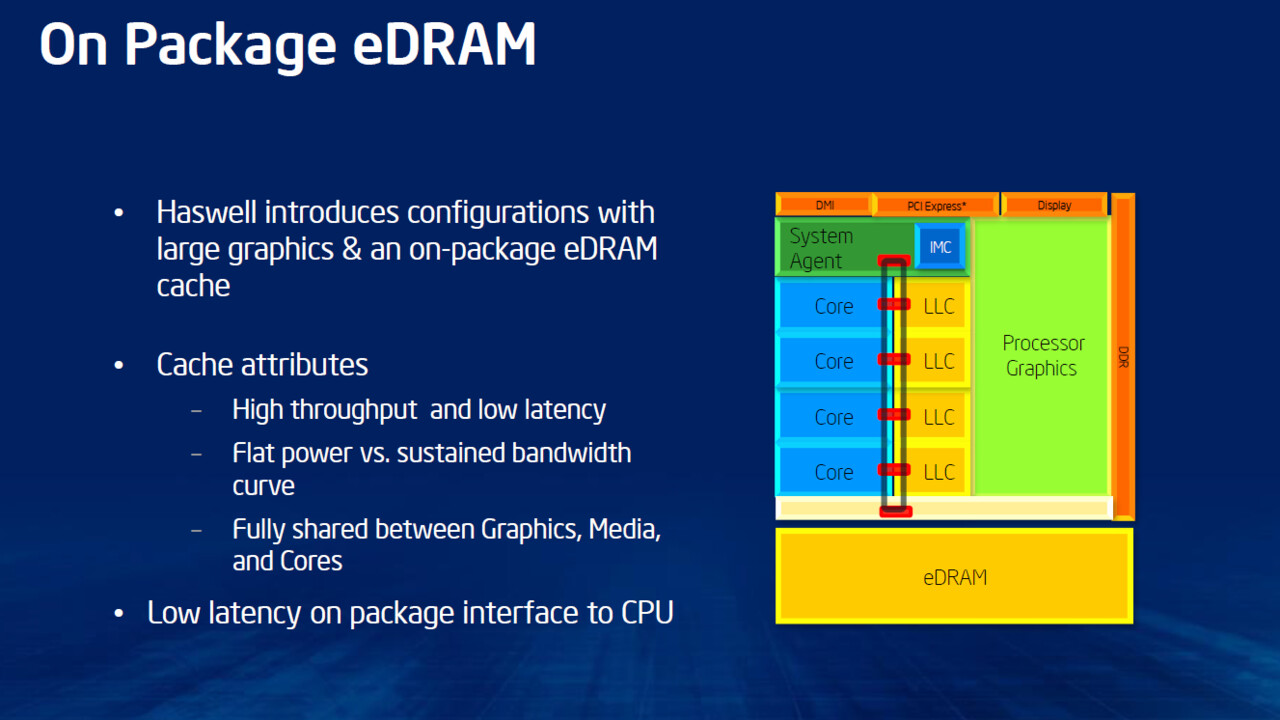

In positiver Erinnerung von Intel ist eben genau die letzte Generation eines „L4-Caches“. Der eDRAM sorgte als zusätzlicher Speicher seit Haswell und darauf folgend in vielen Generationen von Notebook-Prozessoren für zusätzliche Leistung, auch er war wahlweise 32 MByte, 64 MByte oder 128 MByte groß. Für den Desktop gab es nur wenige Ausnahme-Produkte, ein umgelabelter Notebook-Chip in der Haswell-Generation. In besonderer Erinnerung sind jedoch zwei Broadwell-Lösungen aus dem Jahr 2015, unter anderem der Intel Core i7-5775C (Test), der je nach Spieletitel seinen deutlich geringeren Takt dank zusätzlichem Cache mehr als wettmachen konnte.

Wie genau die Umsetzung des L4-Caches in neuer Form erfolgt, soll sich noch im Laufe des Jahres klären. Intel wird Meteor Lake vermutlich im Herbst enthüllen, das Notebook steht hier im Fokus. Genau dort war der eDRAM zuletzt zu finden. Durch diese Entwicklung und auch die vielen anderen erwarteten Neuerungen, könnte sich Meteor Lake zu einem technisch sehr interessanten Produkt mausern. Der Hersteller versucht das schon seit einiger Zeit zu vermitteln und schlägt die Werbetrommel für Intel Meteor Lake bereits seit fast zwei Jahren.

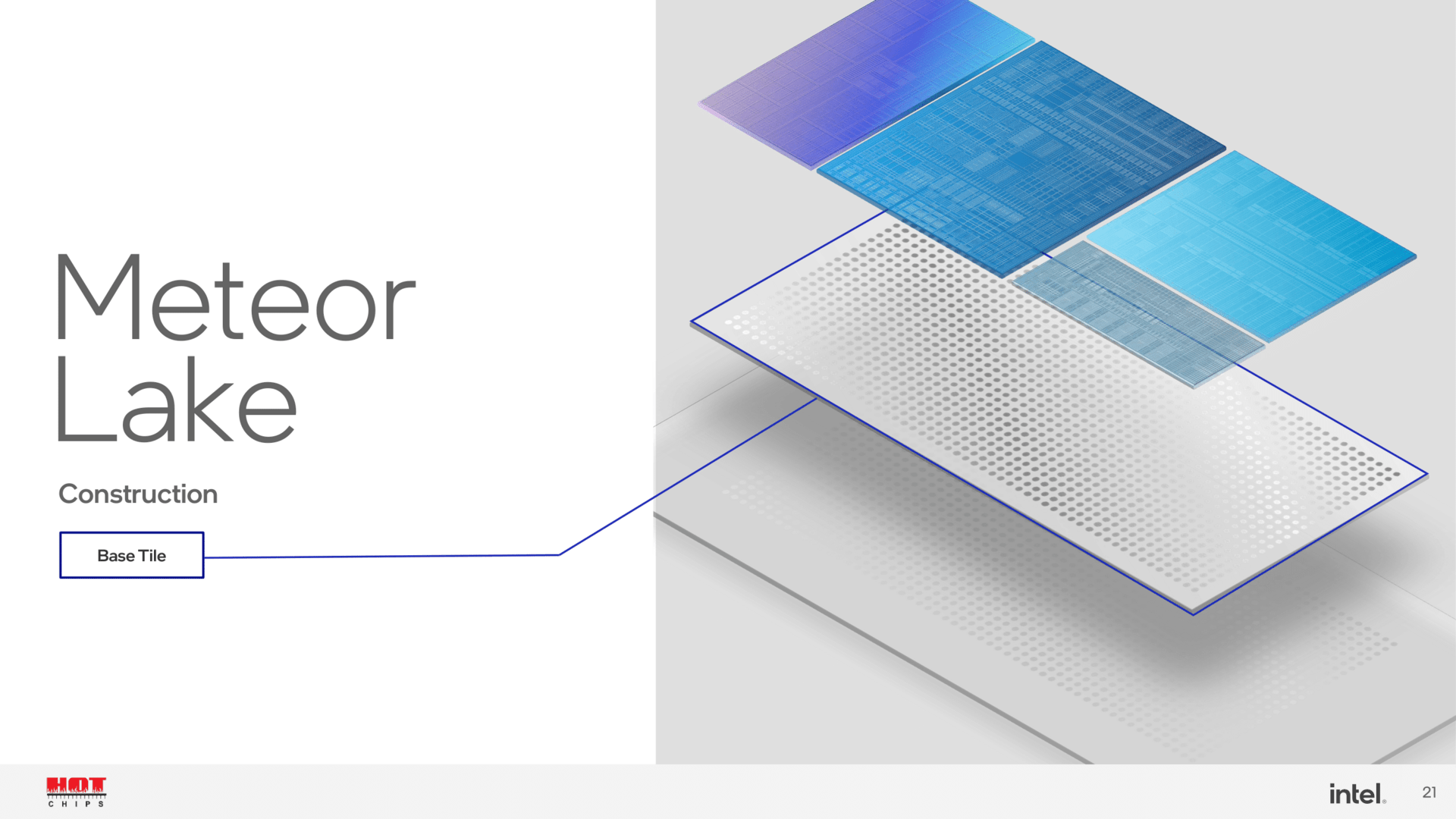

In den letzten Tagen hat sich das Bild vervollständigt, viele kleine Puzzle-Teile wurden zusammengefügt. Dabei zeigte sich, dass die ersten Leaks zu ADM schon ein Jahr zurückreichen, damals wurde „Adamantine“ nur falsch eingeordnet. Nun ist klar, dass dieser L4-Cache ein Teil des Base Tiles werden kann, ein Schaubild aus einem Intel-PDF verdeutlicht dies.

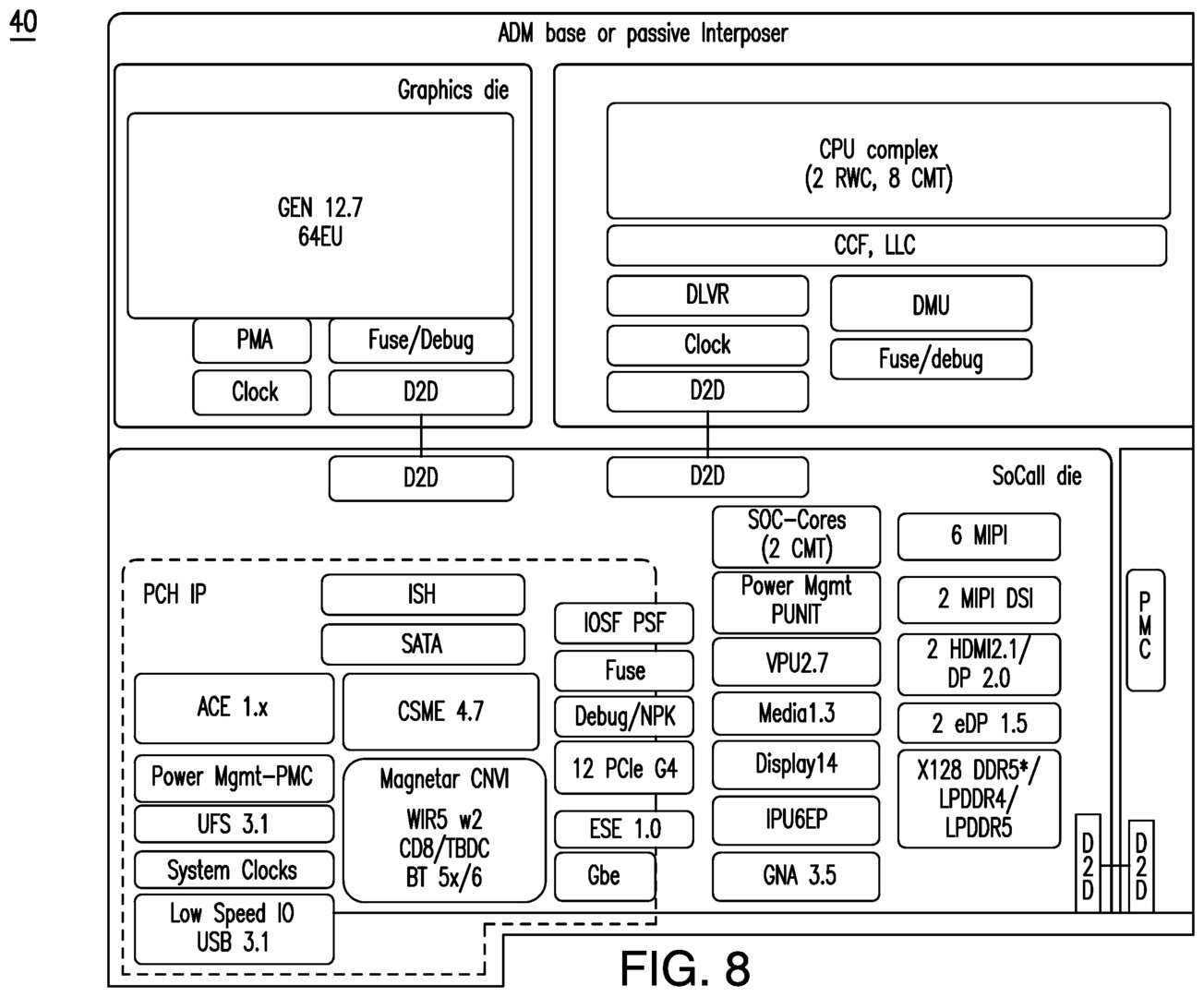

Das Intel-Patent – es wurde vor einigen Tagen auch an ComputerBase herangetragen – reicht dabei bis ins Jahr 2020/2021 zurück und beschreibt einen großen On-Package-Cache. Andere Angaben, beispielsweise zur Anzahl der EUs oder Kernen, sind jedoch oft nur beispielhafter Natur und stehen nicht direkt für ein echtes Produkt. Daran lassen sich deshalb keine Rückschlüsse auf Meteor Lake oder den Nachfolger hinsichtlich seiner finalen Ausstattung ableiten.

[0058] Next generation client SoC architectures may introduce large on-package caches, which will allow novel usages. Access time for the L4 (e.g., "Adamantine" or "ADM") cache may be much less than the DRAM access time, which is used to improve host CPU and security controller communications. Embodiments help to protect innovations in boot optimization. Value is added for high end silicon with higher pre-initialized memory at reset, potentially leading to increased revenue. Having memory available at reset also helps to nullify legacy BIOS assumptions and make a faster and efficient BIOS solution with a reduced firmware stage (e.g., pre-CPU reset stage, IBBL stage and IBB stage) for modern device use cases like Automotive IVI (in-vehicle infotainment, e.g., turn on rear view camera within 2 sec), household and industrial robots, etc. Accordingly, new market segments may be available.