Toshiba und Western Digital: Erst mit BiCS3 und 64 Layer ist 3D-NAND kostengünstig

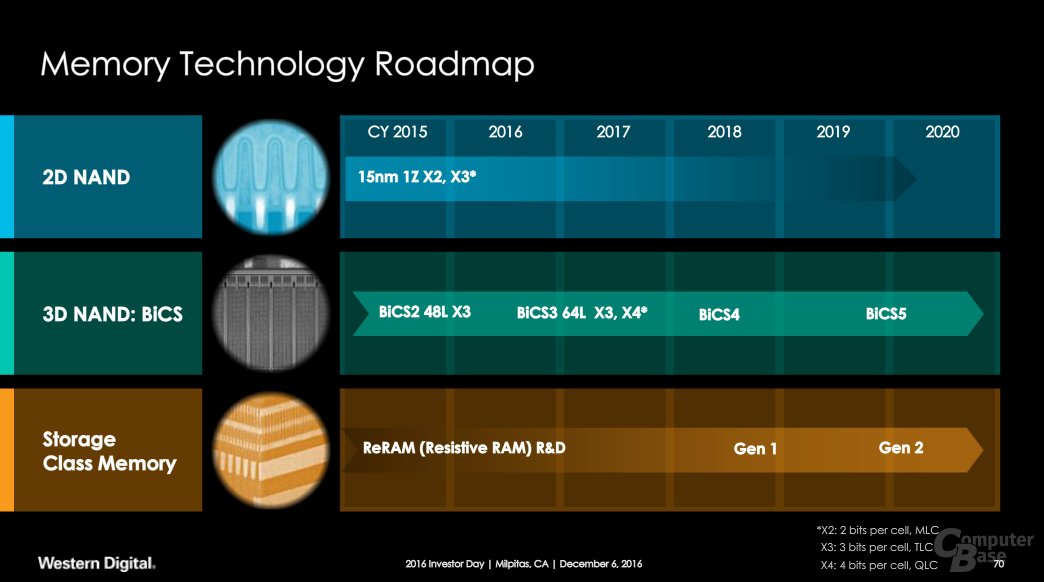

Auf dem Investor Day 2016 von Western Digital war neben HDD-Technik auch Flash-Speicher ein Thema. Siva Sivaram, Executive Vice President Memory Technology, erklärte, warum der aktuelle 15-nm-2D-NAND der branchenweit beste sei und warum sich 3D-NAND für den Hersteller erst jetzt wirklich lohne.

Seit der Übernahme von SanDisk gehört auch Flash-Speicher zum Portfolio von Western Digital. Die bestehenden Flash Ventures zwischen SanDisk und Toshiba hatte das Unternehmen mit übernommen. Somit besteht Zugriff auf 2D-NAND und 3D-NAND für SSDs, Speicherkarten und weitere Produkte. Gemeinsam mit Toshiba wird die Technik weiterentwickelt und am Ausbau der Fabriken gearbeitet.

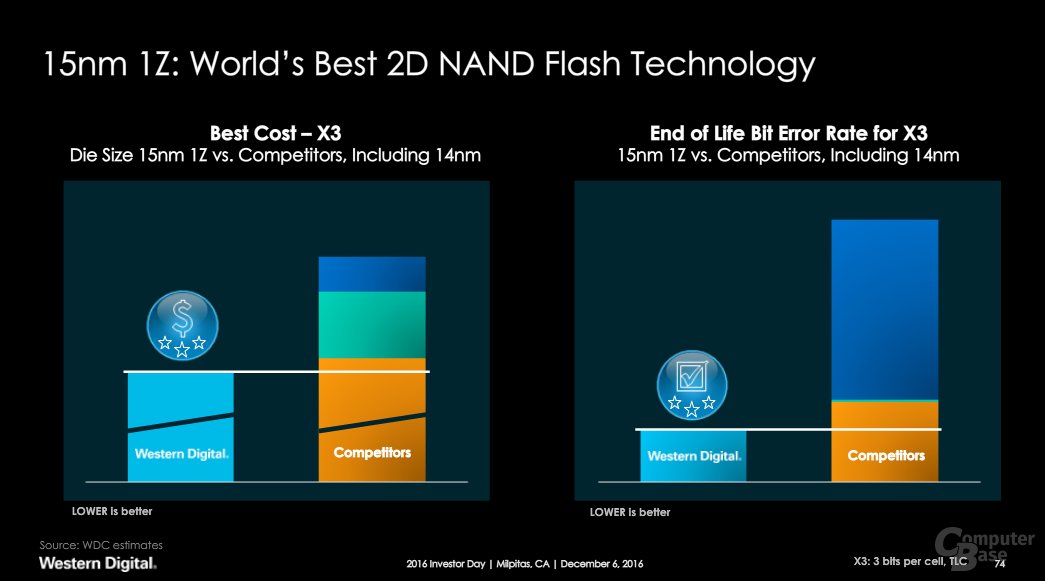

Generation 1Z (15 nm)

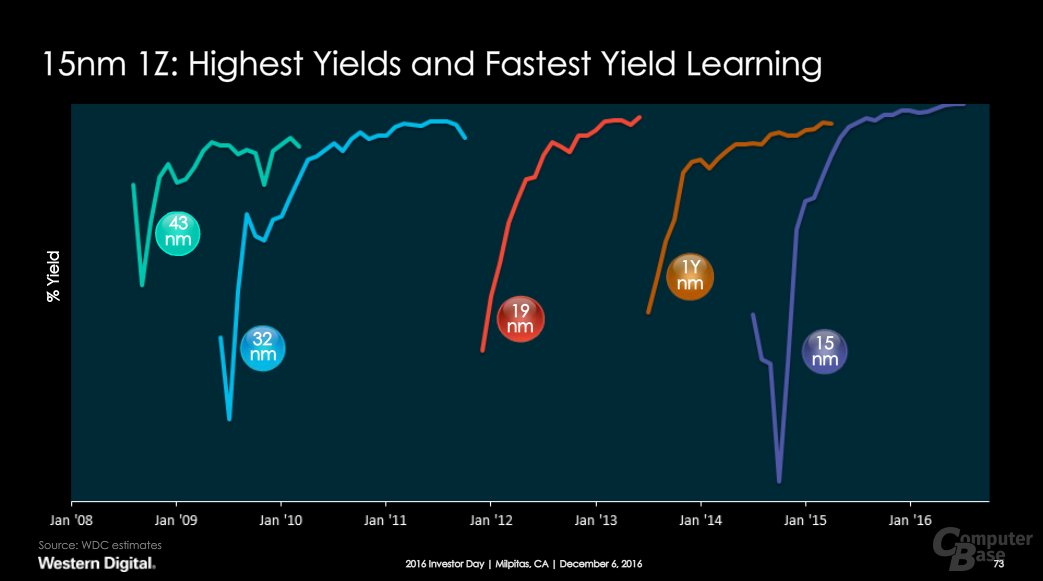

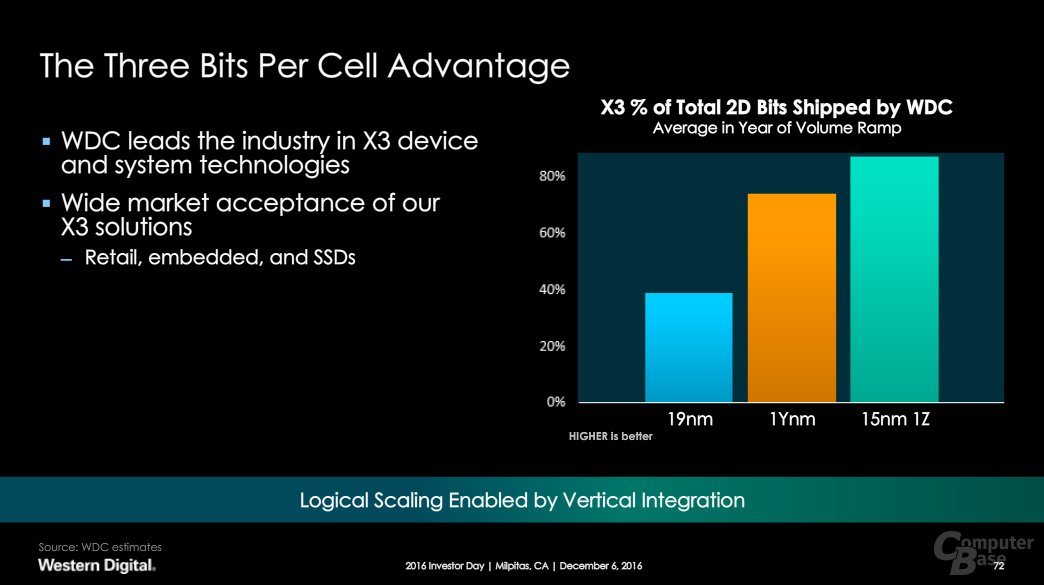

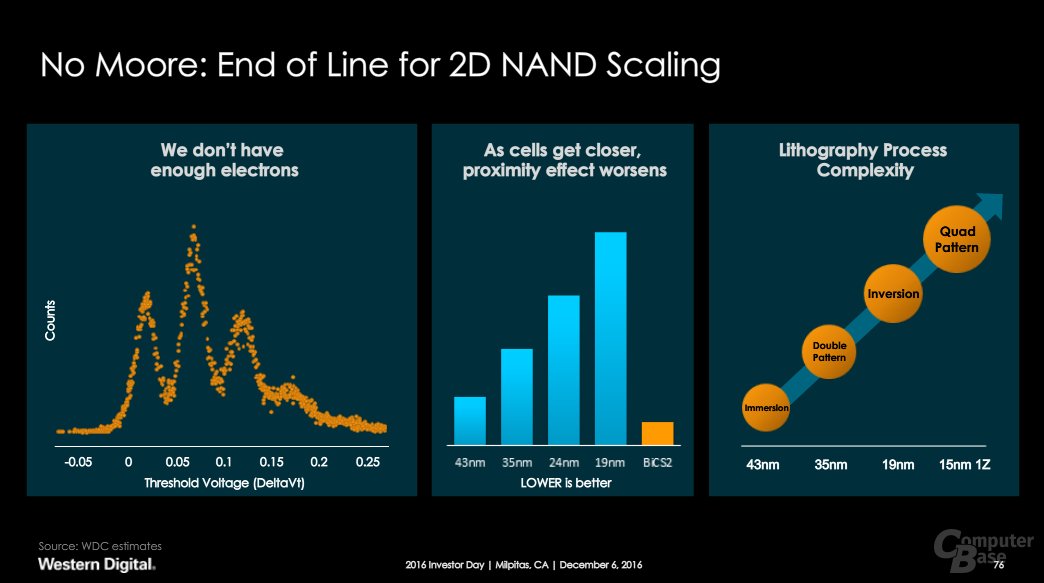

Bevor Sivaram bei der Präsentation vor Investoren und Presse auf 3D-NAND zu sprechen kam, richtete er das Augenmerk auf 2D-NAND der aktuellen Generation 1Z mit 15 Nanometern. Der 15-nm-Flash von SanDisk und Toshiba sei nicht nur der erfolgreichste 2D-NAND für die Unternehmen, sondern der ganzen Branche. Hauptgrund ist die Wirtschaftlichkeit, denn der 15-nm-NAND in der TLC-Variante X3 mit drei Bit pro Zelle ist besonders klein, was für niedrige Herstellungskosten sorgt. Trotz nominell größerer Strukturbreite soll auch Samsungs 14-nm-NAND bei der Die-Fläche geschlagen werden. Auch die Fehlerrate gegen Ende der Lebensdauer sei besser als bei der Konkurrenz.

Der Erfolg des 1Z-Flash beruht auch auf der Fertigung. Der 15-nm-Prozess sei besonders gut angelaufen und habe schnell die bisher beste Chip-Ausbeute (Yield Rate) erreicht. Bereits im ersten Jahr der Massenproduktion habe 80 Prozent des verkauften TLC-2D-NAND der Generation 15nm 1Z angehört. Doch der angeblich „beste 2D-NAND der Welt“ ist zugleich auch die letzte 2D-NAND-Generation des Herstellers, denn eine weitere Verkleinerung ist technisch und wirtschaftlich nicht mehr sinnvoll.

3D-NAND erst mit 64 Layern wirtschaftlich

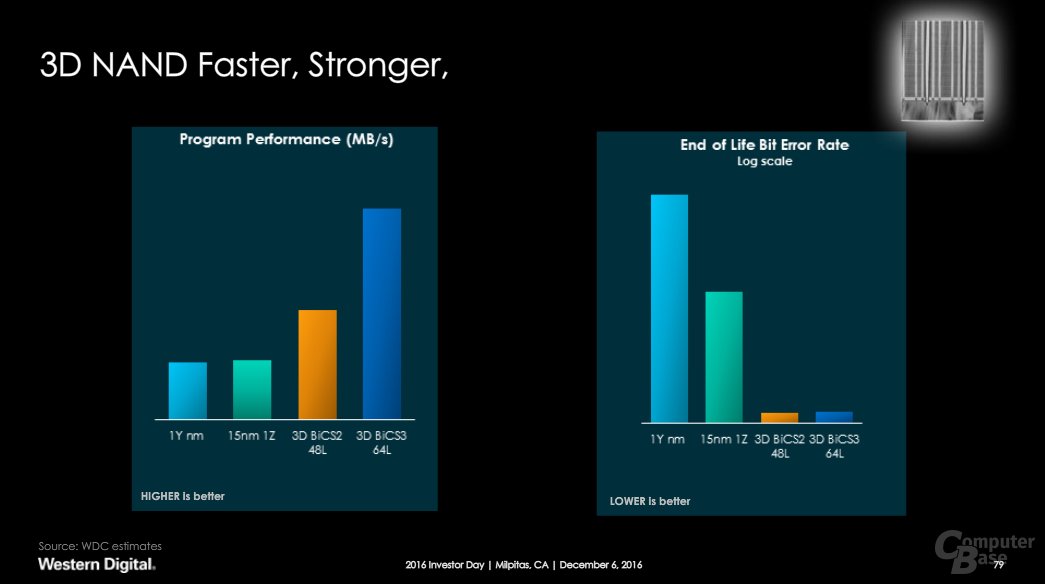

Bei der Herstellung von 3D-NAND hinken alle Hersteller Samsung hinterher. Aus Sicht von Western Digital ist dies anders, denn erst jetzt lohne es sich wirklich 3D-NAND herzustellen. Wie Samsung hätte man schon früher 3D-NAND mit 24 oder 32 Zellschichten auf den Markt bringen können, doch die Kosten seien viel zu hoch gewesen. Aus diesem Grund wurde aus der ersten Generation (BiCS1) kein Produkt. Inzwischen bedienen Western Digital und Toshiba den Markt mit der zweiten Generation des BiCS genannten 3D-NAND. BiCS2 besitzt bereits 48 übereinander liegende Zellschichten und bietet in der TLC-Variante mit 3 Bit pro Zelle (TLC) 256 Gigabit pro Chip, genau wie Samsungs dritte Generation des V-NAND.

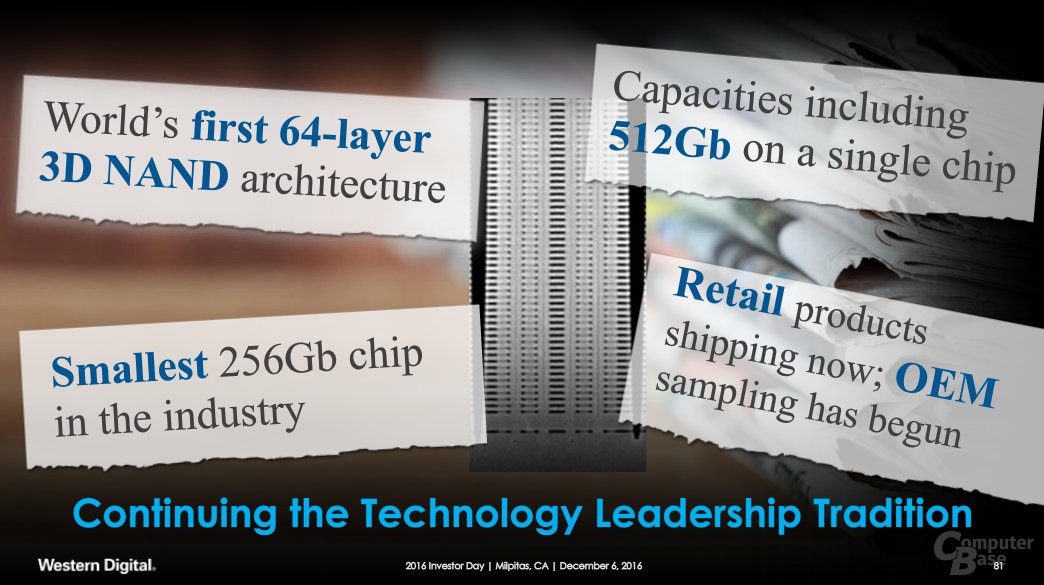

BiCS3 mit 64 Layer wird ausgeliefert

Doch erst BiCS3 mit 64 Zellschichten (Layer) bezeichnet Sivaram als „erste echte kostengünstige Technologie“, die damit aus Sicht des Herstellers auch wirtschaftlich sinnvoll ist. Western Digital verkündet, dass die dritte Generation des 3D-NAND bereits in den Retail-Markt ausgeliefert wird. Mit OEMs laufe bereits die Bemusterung (Sampling). Damit seien Western Digital und Toshiba der Konkurrenz bei 64-Layer-3D-NAND voraus. Samsung hatte im Vorfeld die Serienfertigung der vierten Generation des V-NAND mit 64 Lagen für das laufende vierte Quartal angekündigt.

Kleinste 256-Gigabit-Chips der Branche

Welche Variante von BiCS3 in welchen Produkten eingesetzt wird, beantwortet die Ankündigung jedoch nicht. Bekanntlich war zunächst BiCS3 als TLC-Version mit 256 Gigabit und damit ohne Kapazitätszunahme gegenüber BiCS2 vorgesehen. Doch sollen die Chips nun kleiner und damit die kleinsten 256-Gigabit-Chips der Branche sein, was mehr Chips pro Wafer und niedrigere Kosten bedeutet. Doch klingt es so, als wäre auch bereits BiCS3 mit 512 Gigabit und damit der höchsten Kapazität pro Chip verfügbar. Dies wäre zumindest überraschend, denn mit dem ersten QLC-Speicher mit 4 Bit pro Speicherzelle (X4) ist eigentlich erst ab dem kommenden Jahr zu rechnen.

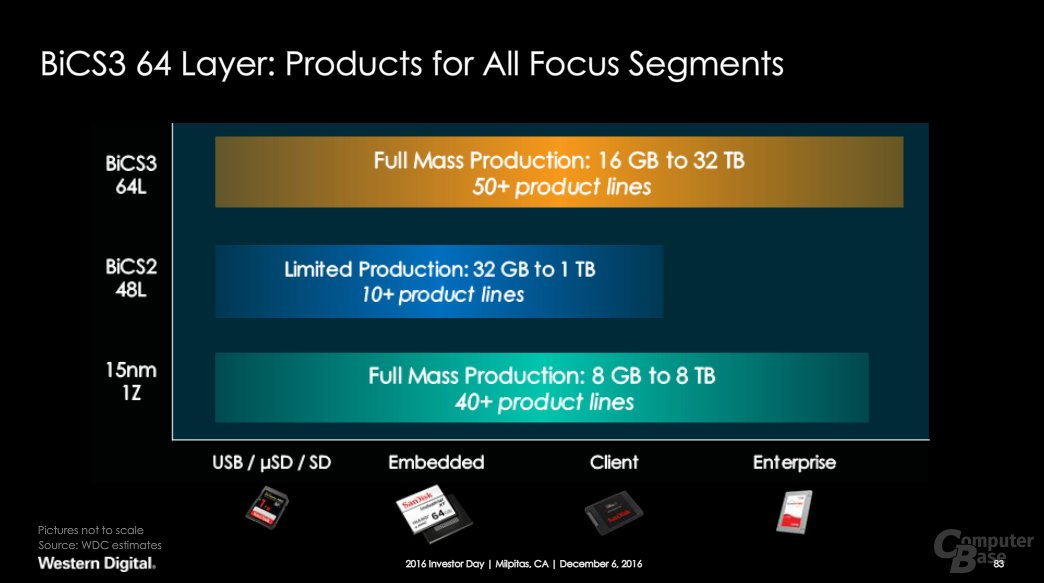

BiCS3 für Produkte mit bis zu 32 TByte

Eine weitere Grafik veranschaulicht, dass BiCS2 nur begrenzt produziert und in Produkten eingesetzt wird. BiCS3 soll hingegen den Stellenwert des 15-nm-2D-NAND erreichen und in über 50 Produktlinien aller Bereiche zum Einsatz kommen. Von der kleinen Speicherkarte oder dem Embedded-Chip mit 16 GByte bis hin zur Enterprise-SSD mit bis zu 32 TByte reicht das anvisierte Einsatzgebiet. Letztlich wird der 3D-NAND von Toshiba und Western Digital damit auch seinen Weg in SSDs für Endkunden finden. Dort sind bisher nur Micron und Samsung mit 3D-NAND vertreten.

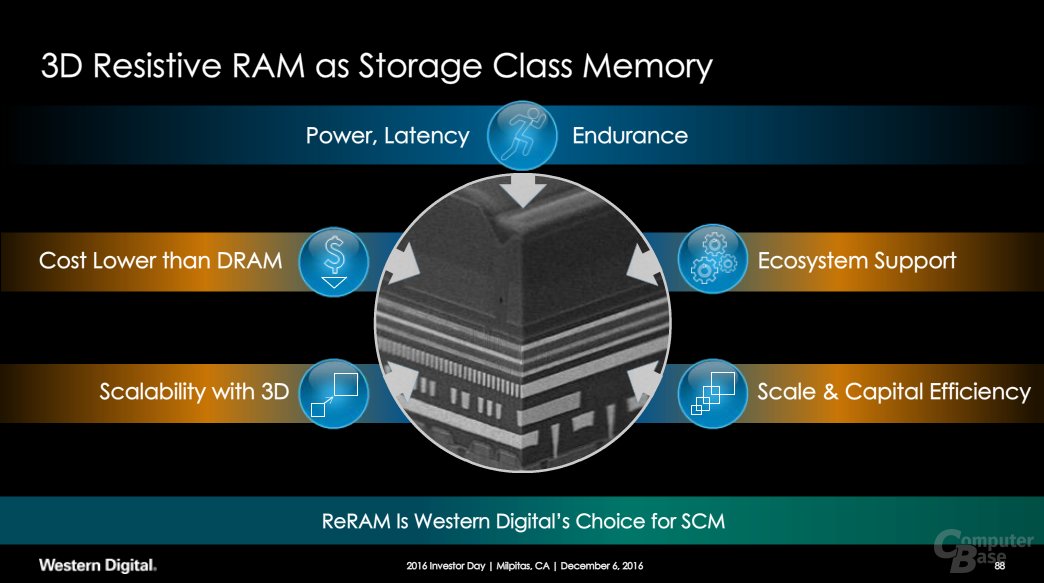

ReRAM als Storage Class Memory

Keine Neuheiten gab es in der neuen Speicherklasse des zwischen DRAM und NAND-Flash platzierten Storage Class Memory (SCM) zu verkünden. Western Digital und Toshiba hatten bereits zuvor in Aussicht gestellt, dass Resistive RAM (ReRAM) ihre Technik der Wahl für SCM sein wird. Die Roadmap datiert die erste Generation auf das zweite Halbjahr 2018.