Intel Cascade Lake-AP: 48 Kerne mit 12-Kanal-DDR4 im Multi-Chip-Package

48 Kerne, 12 Speicherkanäle – Intel Cascade Lake Advanced Performance vereint zwei CPU-Dies auf einem Chip, der zudem auch noch skalierbar über zwei Sockel sein wird. Es ist die Antwort von Intel auf AMD Epyc, deren zweite Generation mit 64 Kernen erwartet wird. 2019 verspricht im Server-Bereich extrem interessant zu werden.

Genau einen Tag vor AMDs Veranstaltung rund um die Thematik Data Center und einem Blick auf die nächste Generation Epyc-Prozessoren mit dem Codenamen Rome, legt Intel vor – ein Déjà-vu zum Sommer. Und die Ankündigung hat es auch heute in sich, denn sie zeigt Intels neuen Multi-Chip-Ansatz im Prozessorbereich, der auf ganz klassischem Wege erfolgt. Dies bedeutet in erster Linie, dass überraschenderweise kein EMIB genutzt wird. Stattdessen kommunizieren die Prozessorkerne über UPI, dem Nachfolger von QPI, so wie die CPUs auch in einem Multi-Sockel-System miteinander umgehen. Dennoch gibt es Unterschiede.

„Glued together“

Vor 16 Monaten begann Intels Marketing gegen AMD zu schießen, die den Multi-Chip-Ansatz für die Epyc-Server-Prozessoren verfolgten. Verächtlich nannten sie die Lösung von AMD, dass sie im Grunde genommen doch vier zusammengeklebte Desktop-Prozessoren sind. Jetzt geht auch Intel wieder zurück zu dem, was vor Jahren auch in der Firma Usus war: Ein Core 2 Quad war schließlich höchst erfolgreich mit „zusammengeklebten Dies“ auf einem Package. Und so erlebt das Vorhaben jetzt eine Wiedergeburt.

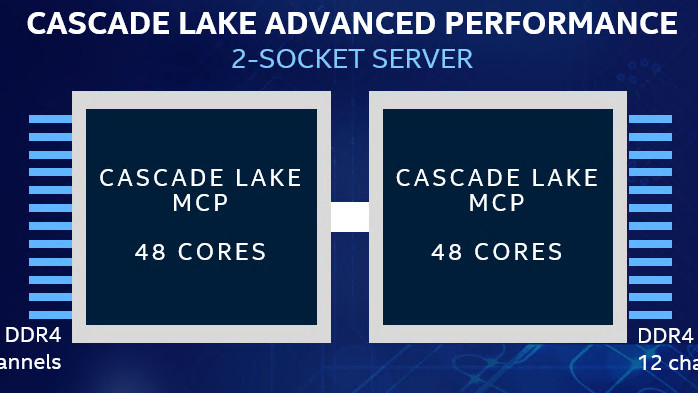

Dafür packt Intel zwei 24-Kern-Prozessoren mit ihrem Sechs-Kanal-Speicherinterface auf ein Package. Wie bei AMD verdoppelt (oder bei AMD auch vervierfacht) sich dadurch all das an technischen Gegebenheiten, was ein Prozessor-Die bereitstellt: Nicht nur die Kerne, allen voran auch das Speicherinterface. 12 Kanäle von Intel suchen in diesem Markt bisher ihresgleichen.

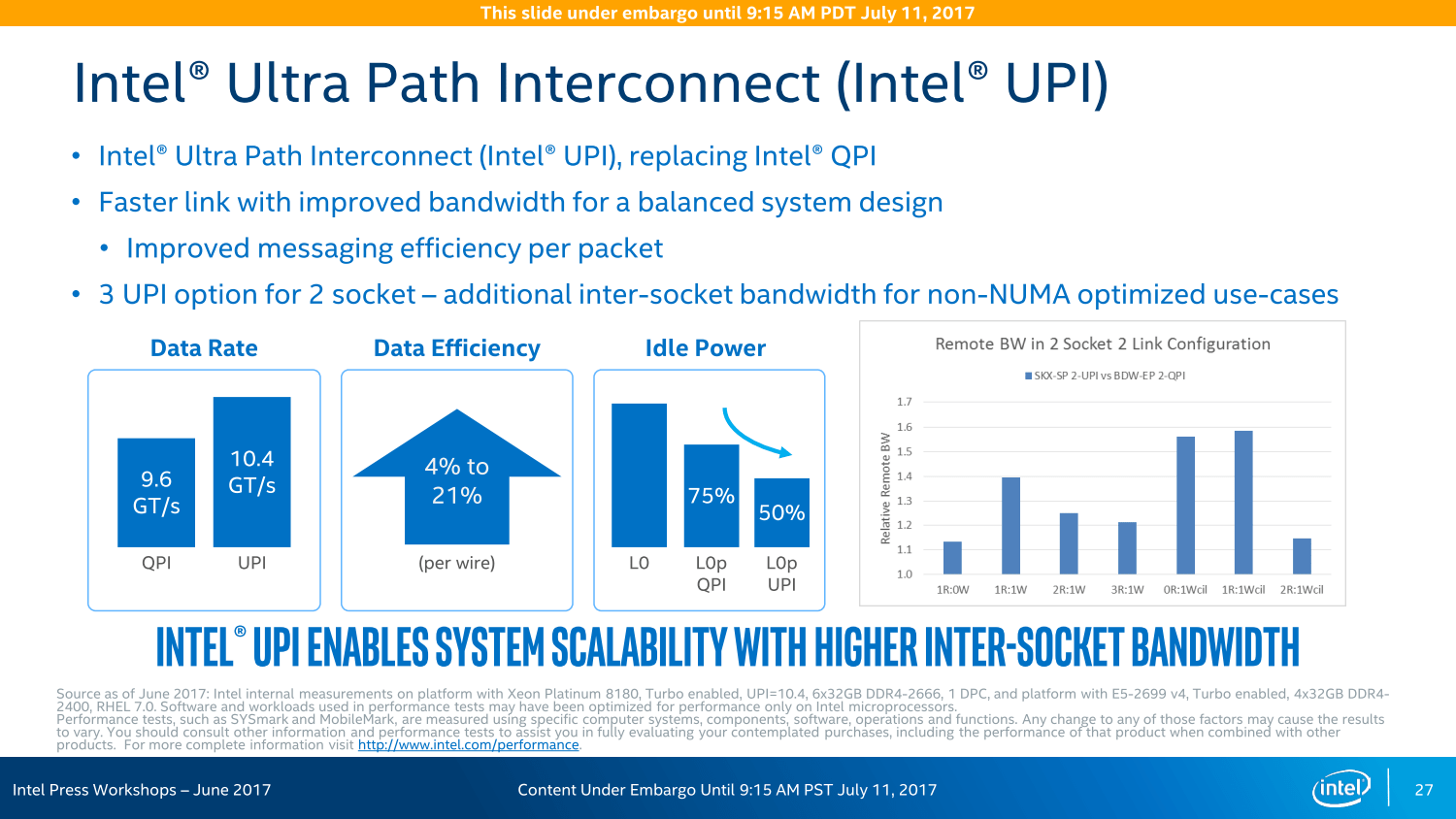

Für die gesamte Kommunikation sorgt Ultra Path Interconnect (UPI). Diesen hatte Intel mit Skylake-SP neu eingeführt und viele Schwachstellen von QPI beseitigt. CPUs mit 3 UPI-Links waren damals bereits explizit für den Einsatz von Systemen mit zwei CPUs gedacht, dementsprechend ist anzunehmen, dass die CPUs auch hier exakt auf diesen Modellen basieren und der jeweils zusätzliche UPI-Link direkt für die Kommunikation auf dem Package abgezweigt wird. Die primäre Zielgruppe der Cascade Lake-AP sind Zwei-Sockel-Systeme, erklärte Intel vorab. Und auch dafür wird noch UPI benötigt, nicht nur für die Kommunikation der zwei Dies auf dem Package sondern auch noch zum zweiten Prozessor mit seinen zwei Dies.

Angesichts dessen wird sich auch Intel mit dem Problem der Latenzen befassen müssen, exakt den Punkt, den sie auch AMD vorwerfen. Wenn Kern 1 im ersten Die Informationen des 24. Kerns im zweiten Die haben will, die dort im lokalen Cache liegen, wie viel Zeit nimmt dies in Anspruch? Das Mesh-System von Skylake-SP arbeitet so, dass alle Abfragen/Auslieferungen multidirektional ausgelegt sind und immer den kürzesten Weg nehmen. Dieser dauert je nach Entfernung aber eine gewisse Zeit: Vertikal mit jeder Reihe ein Cycle, vom Kern zum L3-Cache sind es maximal vier Cycles. Horizontal sieht das anders aus, dort wandern die Daten teilweise über längere Strecken, die Rechnung läuft nach dem Schema 1+3+1+3+ ... ab. Der Ableger mit weniger Kernen hatte so unter Umständen eine höhere Performance, weil die Wege kürzer sind. Um dem wiederum entgegenzuwirken, gibt es die Option auf eine Cluster-Bildung in den größeren Varianten. Dieser Punkt dürfte bei Cascade Lake-AP noch wichtiger werden.

Zwei große Dies auf noch größerem Package

Die Frage nach dem Package ließ Intel bei der Enthüllung von Cascade Lake-AP offen. Auf herkömmlichen, bisher von Intel genutzten Lösungen kann dies keinen Platz finden, denn der Aufbau unterscheidet sich massiv. Allein die zwölf Speicherkanäle, die der Prozessor nun insgesamt zur Verfügung stellt, benötigen viel mehr Pins als dies der Sockel 3647 bisher bieten kann. Ohnehin ist der 28-Kern-Die mit 6-Kanal-Speicherinterface bereits knapp 700 mm² groß, dort gibt es bei Cascade Lake keine Abwandlungen, da Intel nach wie vor auf 14 nm setzen muss. Zwei davon auf einem Package suchen dann bisher ebenfalls ihresgleichen. Der bereits vor einigen Monaten auf der Intel-Homepage gelistete BGA-Prozessor mit 5.903 Kontaktpunkten passt deshalb perfekt ins Bild. Ob es die CPU letztlich aber nur fest verlötet gibt oder auch im klassischen LGA, ist noch unklar. So oder so, es wird vermutlich ein Monster.

Ausblick auf die Leistung

Intels Ankündigung kommt mit einigen ersten Prognosen, was die neuen Produkte leisten könnten. Dabei bezieht sich Intel sowohl auf AMD Epyc 7601, dem 32-Kern-Prozessor des Konkurrenten, als auch den Xeon Platinum 8180 als aktuellem 28-Kern-Flaggschiff aus eigenem Hause. Gemessen an Linpack soll der Vorsprung gegenüber AMD mit dem Faktor 3,4x deutlich sein, bei Stream Triad hingegen mit 1,3x überschaubar gewinnen. Doch die Details im Kleingedruckten fehlen zum großen Teil, auch ist die Leistung von Cascade Lake-AP bisher nur eine Hochrechnung mit dem Stand von Anfang Oktober.

Gegenüber einem aktuellen Xeon Platinum 8180 mit Softwarestand vom Launch der Serie spricht Intel von einer 17-fachen Leistung. Dieser Wert lässt sich leichter einordnen, denn erst kürzlich hatte Intel für die normalen Cascade Lake-SP, die ebenfalls mit 28 Kernen antreten, eine 11-fache Leistungssteigerung versprochen, die durch Zusatzinstruktion VNNI von den Xeon Phi mit dem Codenamen Knights Mill und weitere Softwareanpassungen realisiert werden. 48 Kerne würden demnach noch ein wenig zulegen, aber erwartungsgemäß nicht linear über die Kerne skalieren und zulegen.

Viele Fragen offen, Start 2019

Viele Fragen bleiben heute aber noch ungeklärt, einschließlich des Preises versteht sich. Einige will Intel in der kommenden Woche auf der Supercomuting Conference beantworten, den Rest dann in den kommenden Monaten bis zum Start. Den Starttermin für Cascade Lake-AP gibt Intel für 2019 an (vermutlich erstes Halbjahr), die gesamte Familie soll dort auf einen Schlag vorgestellt werden. Dies ist eine leicht andere Formulierung als bisher, wenngleich Intel betont, die ersten Prozessoren der Cascade-Lake-Familie noch im vierten Quartal 2018 for revenue ausliefern wird. Ein großes Launch-Event wird definitiv erst 2019 abgehalten.

Zur SC18 hat Intel einige weitere Zahlen veröffentlicht. Diese zeigen erneut zwei Cascade Lake-AP mit insgesamt 96 Kernen und 12-Kanal-Speicher gegenüber zwei AMD Epyc 7601. Die von Intel bereitgestellten Zahlen zeigen das gleiche Bild wie zuvor, wenn es im Einsatz auf AVX und vorrangig gute Latenzen ankommt, liegt der Neuling deutlich vorn. Ob das das reale Bild ist, muss Cascade Lake-AP aber ohnehin gegen „Rome“ beweisen: Dort hatte AMD anhand eines ersten, ebenfalls sehr stark selektierten Benchmarks gezeigt, dass ein einzelner Rome-Prozessor mit 64 Kernen mit zwei Skylake-SP Xeon Platinum 8180 fertig werden kann. Wie bei Intel ist aber auch der Wert von AMD mit großer Vorsicht zu genießen.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der Veröffentlichungszeitpunkt.