Colindo schrieb:

Der Artikel ist auch echt interessant. Ich zitiere mal ein paar Stellen:

Bestätigt, dass die Chips von verschiedenen Fertigern kommen, wahrscheinlich damit GlobalFoundries weiterhin gut ausgelastet wird.

Immerhin hat AMD ja auch noch ein Wafer-Agreement zu erfüllen, was sie wohl wegen des ausgefallenen GloFo 7nm-Prozess so verhandelt haben, dass für Zen 2 und 3 die IO-Dies von GloFo kommen, damit genug Wafer abgenommen werden.

Es ist auch sehr interessant, was NICHT beantwortet wurde.

Ich erinner mich zB an das Interview mit David Wang bezüglich MCM-Design bei GPUs.

https://www.pcgamesn.com/amd-navi-monolithic-gpu-design?tw=PCGN1

Statt "Kein Kommentar" oder "warten wir Navi ab" sagte man relativ offen, dass dies für den Gaming Markt im Moment noch nicht absehbar ist.

Was mich wieder zum

Anandtech-Interview führt.

IC: With all the memory controllers on the IO die we now have a unified memory design such that the latency from all cores to memory is more consistent?

MP: That’s a nice design – I commented on improved latency and bandwidth. Our chiplet architecture is a key enablement of those improvements.

IC: When you say improved latency, do you mean average latency or peak/best-case latency?

MP: We haven’t provided the specifications yet, but the architecture is aimed at providing a generational improvement in overall latency to memory. The architecture with the central IO chip provides a more uniform latency and it is more predictable.

IC: Do the chiplets communicate with each other directly, or is all communication through the IO die?

MP: What we have is an IF link from each CPU chiplet to the IO die.

IC: When one core wants to access the cache of another core, it could have two latencies: when both cores are on the same chiplet, and when the cores are on different chiplets. How is that managed with a potentially bifurcated latency?

MP: I think you’re trying to reconstruct the detailed diagrams that we’ll show you at the product announcement!

IC: Under the situation where we now have a uniform main memory architecture, for on-chip compared to chip-to-chip there is still a near and a far latency…

MP: I know exactly where you’re going and as always with AnandTech it’s the right question! I can honestly say that we’ll share this info with the full product announcement.

=> Heisst für mich: Generelle Zugriffszeit verbessert, aber wohl nicht von allen Cores gleich. Die Frage ist, ob zumindest die benachbarten Chiplets mit einander verbunden sind. Ansonsten müsste jedes Chiplet wirklich über die IO gehen. Ich bin sehr gespannt wie man das gelöst hat.

Bezüglich der ständigen Frage, wo man hier im Forum schon seit nem Jahr diskutiert: 2 x 4Core-CCX oder ein 8-Core CCX?

Ich hatte mich bereits

vor einem Jahr festgelegt: Es werden 8 Kerne. Mit dem feinen Unterschied, dass diese auf 2 statt auf einem Die untergebracht sind. Ob man das Ganze jetzt über ein CCX oder anders regelt, ist im Grunde nebensächlich. Es werden aber Ganz sicher nicht 2* 4-Core-CCX , wie von einigen behauptet.

Warum nicht?

Schaut Euch doch mal die Form des Zen2 Core-Die an und daneben ein Zeppelin-Die mit 2 CCX:

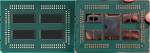

Ich habe da nochmal ein Die-Shot vom Zeppelin zur Veranschaulichung:

Der Zeppellin die ist aufgrund der 2 CCX stark rechteckig, während der Zen2-Core nur leicht rechteckig ist.

Noch ein Beispiel gefällig?

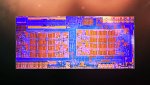

Hier ein Dieshot des 9900k-8Kern Prozessor:

Blau könnt ihr Euch Wegdenken, da IGPU.

Rot bitte auch zum größten Teil wegdenken, da IO-Zeug, welches bei Zen 2 ins IO-Die wandert.

Es bleibt fast nur noch die IF-Fabric.

Jetzt nehmen wir mal nur die Cores+ ein bisschen IO an der Seite für die "virtuelle IF" des 9900k und vergleichen mal mit nem Zen2-Die, wobei wir zwar shrinken, aber das Seitenverhältnis beibehalten....und oh wunder. Das ist von der Form "fast" identisch (Zen2 ein wenig quadratischer).

Sowas ist meiner Meinung nach mit 2 CCX auf einem Die nicht zu bewerkstelligen.

Weiter zum Interview. Sehr gut fande ich auch die Frage zum IO-Die.

IC: The IO die as showed in the presentation looked very symmetrical, almost modular in itself. Does that mean it can be cut into smaller versions?

MP: No details at this time.

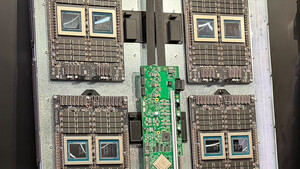

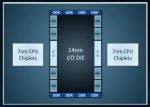

Was mit Symmetrisch gemeint ist?

Bitteschön:

Natürlich ist es nur ein Schaubild, aber man erkennt die Anbindung für Octo-Channel und die beschriebenen 8 IF-Verbindungen für die 8-Dies. Ich vermute auch 128 PCIe-Lanes

Jetzt denken wir einmal scharf nach und wissen, dass Threadripper, "nur" Quadchannel nutzt, aber der Sockel im Grunde gleich ist.

Wir wissen auch, dass das IO-Die mit >300mm relativ groß ist. Was also tun bei Teildefekten des IO-Die selbst?

Richtig! Man benutzt die funktionierende Hälfte für Threadripper!

Beim alten Threadripper wurden ja Dummy Dies eingebaut, damit man die Stabilität unter dem HS erhalten wollte. Mit 4 Dies, die jeweils 4,6 oder 8 Kerne aktiviert haben und einem teildefekten IO-Die könnte man auf Dummy-Dies verzichten. Die Frage ist halt wie die Dies an das Speicherinterface angebunden sind. Möglich wäre auch, dass wirklich die komplette obere oder untere Hälfte abgeschaltet ist. Aber dann müssten evtl. alle 4 Dies in der oberen oder unteren Reihe aktiviert sein und die andere Reihe hätte wegen der Stabilät und Symmetrie wieder 4-Dummy Dies. Fände ich nicht so flexibel.

Threadripper 3000 bekommt dann also im Vollausbau wieder (4*8=) 32 Kerne, aber diesmal ohne Speicherinterface-Verkrüppelungen. Beginnen würde ich bei (4*4) 16 Kernen und in der Mitte dann (4*6) 24 Kerne. Insgesamt nur 3 Modelle, aber die haben es jeweils in sich! Ob auch Modelle mit (4*3) 12, (4*5), 20, oder (4*7) 28 Kernen möglich sind, ist schwer zu beantworten ohne die genauen Restriktionen der Architektur zu kennen. Ich glaube aber 6 Modelle wären ein bisschen viel. Threadripper Gen 1 hatte 3 Modelle und der aktuelle 4, welche wiederum in 2 Kategorien aufgeteilt sind. 6 Modelle für TR Gen 3 wären glaube ich Overkill.

Vielleicht ist es möglich aber die Dies mit 3 und 5 funktionierenden Kernen verwendet man für AM4?!

Da Ganze hätte dann auch wieder 64 PCIe-Lanes.

Kommen wir letztendlich zu Zen 2 für AM4 alias Ryzen 3rd Gen.

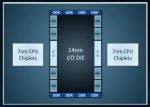

Hier glaube ich wird genau 1/4 des IO-Dies wiederfinden, da es wohl symmetrisch aufgebaut ist (siehe oben).

D.h. 2 IF-Verbindungen für 2 Dies und max. Dual Channel mit 32 PCIe-Lanes.

Wie könnte man sich das Ganze optisch Vorstellen?

Ungefähr so:

Möglich wären hier also bis zu 16 Kerne, wobei ich davon ausgehe, dass man nur bis 12 Kerne geht, um die komplett funktionierenden Dies nicht für Consumer-CPUs zu verschwenden, sondern für Epyc 2 zu nehmen.

Apropo funktionieren... wie oben beschrieben könnte man Dies mit funktionierenden 3 und 5 funktionierenden Kernen für 6 und 10-Kern-CPUs verwenden, wenn dies von der Architektur her möglich ist.

Insgesamt würde sich also folgendes Lineup ergeben:

2 cores per die –> 4-core Ryzen 3400

3 cores per die –> 6-core Ryzen 3500

4 cores per die –> 8-core Ryzen 3600

5 cores per die –> 10-core Ryzen 3700

6 cores per die –> 12-core Ryzen 3800

Die Namensgebung ist natürlich pure Spekulation

Auf die APUs möchte ich nicht wirklich stark eingehen, da ich hier nichtmal weiss, ob die IO-Die Geschichte Sinn macht. Dürfen gerne andere Übernehmen

Wenn es aber ein IO-Die gibt, dann wird man zusätzlich ein 8-Core Chiplet und ein Navi-Chiplet sehen.

Das Core-Chiplet wird anfangs aber nur max. 6 aktivierte Kerne haben. Beim Navi-Chiplet wird man wohl auch ein wenig in Richtung geringere Leistungsaufnahme gehen. Also keine Verdoppelung der Einheiten wie von Vega 11 auf Navi 22, sondern eher Navi 14,vielleicht 16. So hätte man mehr Leistung und dennoch einen geringeren Verbrauch, was grade im Notebook-Segment ja sehr wichtig sein wird.

Vielleicht als letztens noch ein Wort zu Zen3:

IC: AMD has already committed that Milan, the next generation after Rome, will have the same socket as Rome. Can you make the same commitment with Zen 4 that was shown on the roadmap slides?

MP: We’re certainly committed to that socket continuity through Milan, and we haven’t commented beyond that. Obviously at some point the industry transitions to PCIe 5.0 and DDR5 which will necessitate a socket change.

IC: So one might assume that an intercept might occur with Zen 4?

MP: No comment (!)

Ich sagte ja bereits für Zen 2 wird es im AM4 max. 12 Kerne geben, aufgrund der teuren 7nm-Fertigung und Yields. voll funktionsfähige Dies werden für Epyc und Threadripper gebraucht.

Mit Zen3 wird aber 7nm+ verwendet. Man sollte hier keine Wunder erwarten, was Performance angeht.

Ziel ist hier durch den Einsatz von EUV bessere Yields und weniger Belichtungsschritte zu erzielen, was die Produktion DEUTLICH günstiger macht.

Dadurch könnten wir dann mit der Generation Ryzen 4XXX doch noch 16-kerne für AM4 bekommen, bis es danach mit Zen 4 einen neuen Sockel mit PCIe 5 und evtl. DDR5 gibt

Sorry für die Wall of Text, aber ich wollte einfach mal meine Gedanken zum Anandtech-Artikel, der Next Horizon-Veranstaltung und deren Auswirkung auf Consumer-Produkte in einem Beitrag zusammenfassen

___________

Edit: Witzig... Jim von AdoredTV hatte wohl sehr ähnliche Gedanken wie ich. Auch wenn ich der 16-Core Spekulation widerspreche. 16 Kerne werden wir erst mit Zen3 in 7nm+ sehen.