Stannis

Lieutenant

- Registriert

- Juli 2011

- Beiträge

- 549

Hi.

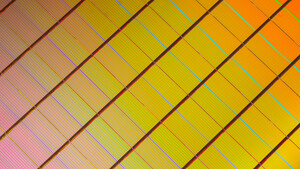

Ich arbeite mich z.Z. in die Arbeitsweise vom RAM an (Rows, Banks, DIMMs, Spalten-Zeilen-Addressen etc. etc.)

Was Ich mir selbst bisher noch nicht ganz beantworten konnte:

Holen moderne PCs immer nur Byte für Byte aus dem Speicher in die CPU-Register, oder ist man heute in der Lage mehrere Bytes gleichzeitig zu laden?

Für mich sieht der Addressaufbau im Moment so aus, als würde zumindest bei 32-Bit-Systemen immer nur ein Byte zur gleichen Zeit aus dem Speicher geholt werden können.

Ich lass mich da gern aufklären. Bisher wundert mich, warum man sich dann überhaupt die große Mühe macht die einzelnen Speicherchips noch in Bänke zu unterteilen.

Ich arbeite mich z.Z. in die Arbeitsweise vom RAM an (Rows, Banks, DIMMs, Spalten-Zeilen-Addressen etc. etc.)

Was Ich mir selbst bisher noch nicht ganz beantworten konnte:

Holen moderne PCs immer nur Byte für Byte aus dem Speicher in die CPU-Register, oder ist man heute in der Lage mehrere Bytes gleichzeitig zu laden?

Für mich sieht der Addressaufbau im Moment so aus, als würde zumindest bei 32-Bit-Systemen immer nur ein Byte zur gleichen Zeit aus dem Speicher geholt werden können.

Ich lass mich da gern aufklären. Bisher wundert mich, warum man sich dann überhaupt die große Mühe macht die einzelnen Speicherchips noch in Bänke zu unterteilen.