- Registriert

- Juni 2001

- Beiträge

- 19.907

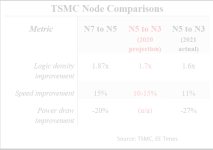

Ja, aber dafür brauchen sie ja die neue Fab die quasi exklusiv N3 baut. N4P läuft in den "alten" N5-Fabs , wovon sie viele Ausbauphasen mittlerweile haben und mehr Kapazität bieten, deshalb da am Ende auch der Preisvorteil. Jetzt gehen die Mainstream-Sachen ja auch erstmal auf N6 als beste Evolution von N7, AMD geht mit einigen PC-Teilen beispielsweise dahin. Denn N6 ist zu N5 heute das, was N4P später zu N3 ist.