'Xander schrieb:

Intel hatte überhaupt zuerst geklebt- und da wurde seites Amd auch gelästert.

Wo bei Kleben oder nicht total irrelevant ist.

Ja, Intel hat zuerst geklebt und ja, AMD hat damals darüber gelästert, nur war damals das "Zusammenkleben" von Intel noch ein Stück anders als AMD bei Zen und nun auch Zen2 und 3.

Intel hat damals 2 CPU-Dies auf ein Package gesetzt, beide CPUs waren aber getrennt vorhanden und konnten nicht direkt miteinander kommunizieren, sondern mussten über das über die Northbridge und damit über den FSB.

Beim »Arbeitsspeicher« hatte das damals keine Nachteile, da der eh über die Northbridge angebunden war, aber wenn beide Dies was wollten, mussten sie sich den FSB teilen.

YforU schrieb:

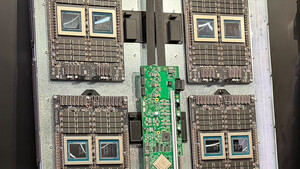

NUMA halte ich bei Sapphire Rapids (pro Socket) für nicht wahrscheinlich. Die Bandbreite zwischen den vier Chiplets dürfte aufgrund von EMIB sehr viel höher sein und die Latenz gleichzeitig um Faktoren geringer.

Nur das EMIB für die Bandbreite nicht der entscheidene Faktor ist, sondern die UPI und wie diese ausgelegt wird, ob man darunter nun EMIB schnallt. UPI wird jetzt auf 16GT/s gesteigert und 4 Links, das kann man auch über weitere Strecken machen.

Der EMIB ist dafür da, dass man die Wege kurz hält und damit die Latenzlaufzeit, und ja die wird vermutlich geringer ausfallen zwischen den vier Dies, nur würde das nicht unbedingt eine eigenwillige NUMA-Konfiguration verhindern wie bei Zen 1, denn dafür wiederum entscheidend ist nicht nur die Bandbreite - die hatte IF über PCIe durchaus gehabt - oder die Latenz - die war grausam - sondern in dem Fall auch die Tatsache, dass man die Daten für die CPU auch in dem Arbeitsspeicher haben wollte, der ohne Umweg angesprochen wird.

Dazu ist es auch wichtig, wie die einzelnen Komponenten als Nodes im Mesh organisiert sind, gibt es einen I/O-Part aus UPI-Links, RAM, PCIe und Rest, oder sind die I/O-Parts einzelne Nodes usw. Und da kann - auch wenn die Latenzen niedriger sind - durchaus sinnvoll erscheinen diese eigenen willige NUMA-Konstruktion des Zen 1 zu nutzen.

AMD hat aktuell zwar etwas längere Signallaufzeit zwischen den Chiplets und dem I/O, kann das aber durch L3-Cache kompensieren und die Latenzen sind vorhersehbar für alle Nodes. Bei der neuen Intel-CPU kann es aber unvorhersehbar werden mit dem RAM, wenn man ggf. über mehre CPUs springen muss um die Daten zu bekommen.