genau. Was es ja auch muss, denn schließlich heißt weniger Platz ja auch weniger Fläche um Wärme abzutransportierenNitschi66 schrieb:Nicht ganz. Die Kerne sind primär auf platzeffizienz getrimmt, was dann aber auch eine leichte effizienzoptimierung mitbringt. Einerseits, weil für die Platzeffizienz weniger Transistoren (die für hohe Taktungen nötig sind) verbaut werden und andererseits weil durch die Taktsenkung das ding etwas mehr im Sweetspot läuft.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News AMD Phoenix2 mit Zen 4 & 4c: Die erste big.LITTLE-APU erblickt heimlich das Licht der Welt

Heise EDIT: Die Quelle schreibt, dass die C Cores in etwa bei 2GHz von der Effizienz umkippen. Sprich kleiner 2GHz sind die C Cores effizienter, größer 2GHz nicht. C Cores mit viel Takt (bis zu 3,5GHz) wird der Energieeffizienz also nicht gerade förderlich sein. Der Flächeneffizienz aber schon - das ist gerade im Low Cost Bereich für AMD ein sehr relevantes Thema, weil sie eben nur die riesen Trümmer von 8C APUs (bis Zen3) hatten und das für alle Mobile Geräte her halten durfte. Das ist wahrscheinlich maßgeblich auch der Grund, warum man noch alte Zen2 Versionen weiterhin neu auflegt - die sind einfach kleiner und kosten weniger in der Herstellung.modena.ch schrieb:Sprich Zen 4C ist um die 3Ghz und ein paar Zerquetschte etwa 30% sparsamer als Zen 4.

Das ist jetzt nicht gar so schlecht mit ziemlich Zen 4 IPC und komplettem Befehlssatz für leichte Aufgaben.

Oder für Cloud Server und Ähnliches.

Warum nicht?modena.ch schrieb:Da ist ein E-Kern mit Skylake IPC doch gar nicht vergleichbar.

https://substackcdn.com/image/fetch/f_auto,q_auto:good,fl_progressive:steep/https://substack-post-media.s3.amazonaws.com/public/images/9ef557e3-9436-407c-a915-6f6872be9f44_683x868.png

Der E-Core mit in etwa Skylake IPC ist halt auch nur ca. 1/4tel so groß, sodass man vier dieser Cores auf die Fläche eines P-Cores unter bringt. Das heißt, du bekommst 100% mehr Threads ggü. einem P-Core mit SMT. Oder anders ausgedrückt, 8x P-Cores bei gleichem Takt sind ca. 30-50% schneller als 8x E-Cores, benötigen aber 4x so viel Fläche. Die Leistungsdifferenz steigt natürlich bei steigendem Takt weiter an. ~4GHz auf den E-Cores vs. 5GHz+ auf den P-Cores, aber wir sind immernoch weit weg von Faktor 4, wie die Flächeneinsparung.

Am Ende kommt das in der effektiven Performance ca. auf ähnliches Niveau wie AMDs Zen4C "Abspeckung". Denn dort sinkt die Performance nicht ggü. dem Zen4 Core. Dafür spart man aber auch nur ca. 30% der Fläche und hat obenraus ein Taktlimit.

Ein E-Core only Intel Design könnte mit um die max. 4GHz also theoretisch ohne mehr Fläche auf 48C/48T kommen - analog einem 13900er. Das ist winzig wenn man das mal ggü. einem 48 Core Epyc vergleicht. Skaliert man das auf ein Maximum, so wäre bei den riesen Trümmern von AMD und Intel im Server Bereich da dicke mittlere 3-Stellige Core Anzahlen möglich, mit inkl. der entsprechenden Leistung bei Software die 1:1 skaliert.

Zuletzt bearbeitet:

Kokuswolf schrieb:So ein Quatsch!

Es geht nicht um IPC, sondern um große und kleine Chips. IPC ist nur ein Merkmal eines Prozessors und statt geringere IPC und weniger Features spart AMD hier an Takt um vier kleinere, weil dicht gepacktere, Zen 4c-Cores herstellen zu können. Diese können dann zusammen mit zwei größeren Zen 4-Cores auf den Die.

Im Bild sieht man das Big/Little buchstäblich:

Anhang anzeigen 1396834

Hart daneben ist deine Verwechslung was die großen und kleinen Cores genau machen. CB hat das klar formuliert:

Setz dich doch bitte mit big.LITTLE auseinander:

Es werden CPU Kerne kombiniert die sich nicht nur im Takt, sondern auch in den IPC unterscheiden UND in der Architektur. Ähnlich dem P und E Core System bei Intel, da werden eben Prozessoren kombiniert die "weit" auseinander liegen was die Architektur angeht.

Snapdragon 8 Gen 2 bringt sogar 4 verschiedene CPU Kerne ins Spiel. Teilweise Only 64Bit, Teilweise 32 und 64 Bit unterstützung.

AMD "Downsized" die Zen4 Cores, das sorgt dafür das WENIGER Takt anliegen kann (weil weniger Spannung) aber der Kern (Zen4c), Grundlegend, seinem ZEN 4 "Bruder" entspricht.Selbst CB hat es verstanden und schreibt es ja sogar!!

Es sind, die GLEICHEN Features, mit weniger Takt und weniger SpannungDas ändert aber nichts an der Feature-Palette, die ist exakt die gleiche.

big.LITTLE + Intel P und E Cores

: geänderte Features, weniger Takt, weniger Spannung, andere Architektur (GRUNDLEGEND)

AMD Zen und Zenc

: gleiche Features, weniger Takt, weniger Spannung, LEICHT geänderte/angeordnete Architektur

und CB Unterstreicht es ja gleich NOCHMAL:

24 Threads werden dank SMT-Unterstützung auch auf den Zen-4c-Kernen damit realisiert. Intels E-Cores bieten bis dato kein SMT.

Intel E und P Cores = kein SMT bei E Cores

AMD Zen und ZenC = SMT für alle, weil "baugleich" und gleiche Features.

Das einzige wo big.LITTLE "okay" wäre wenn man sich auf die physikalische größe bezieht... aber mit dem Konzept wie es ARM lebt hat das einfach nicht so viel zutun...

Edit1:

big.LITTLE wäre bspw. die Kombination aus ZEN4 und ZEN1 wobei die ZEN1 Prozessoren massiv auf Stromsparen getrimmt sind oder ähnliches...

Dann wären wir sehr nah bei Intels P und E Cores ansatz.

Zuletzt bearbeitet:

"Features", bzw. die Ausführbarkeit bestimmter Software sind keine sinnvollen Unterscheidungsmerkmale für Mikroarchitekturen. (unterschiedliche Mikroarchitekturen können identische Software ausführen, identische Mikroarchitekturen durch selektive Deaktivierung davon abgehalten werden)

- Registriert

- Dez. 2004

- Beiträge

- 3.779

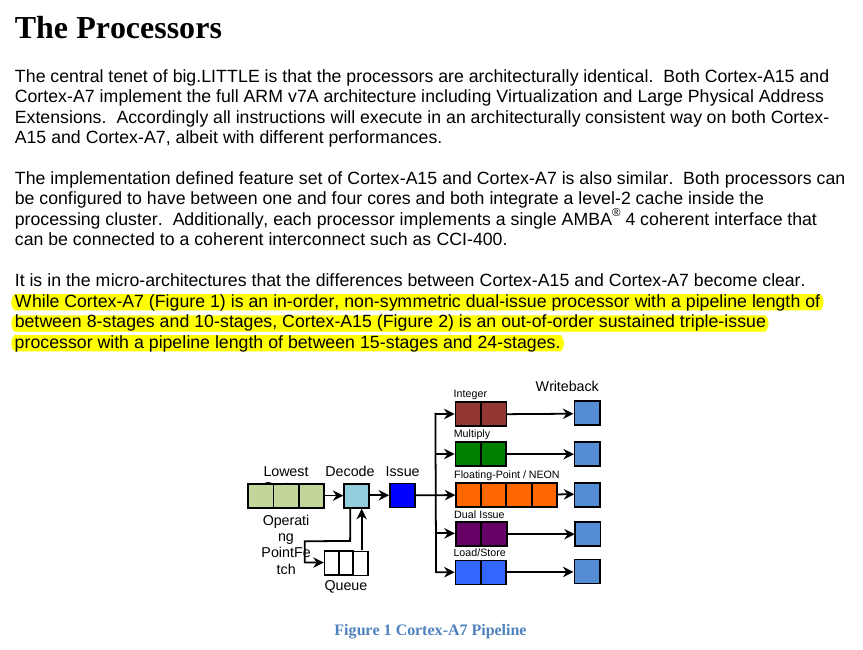

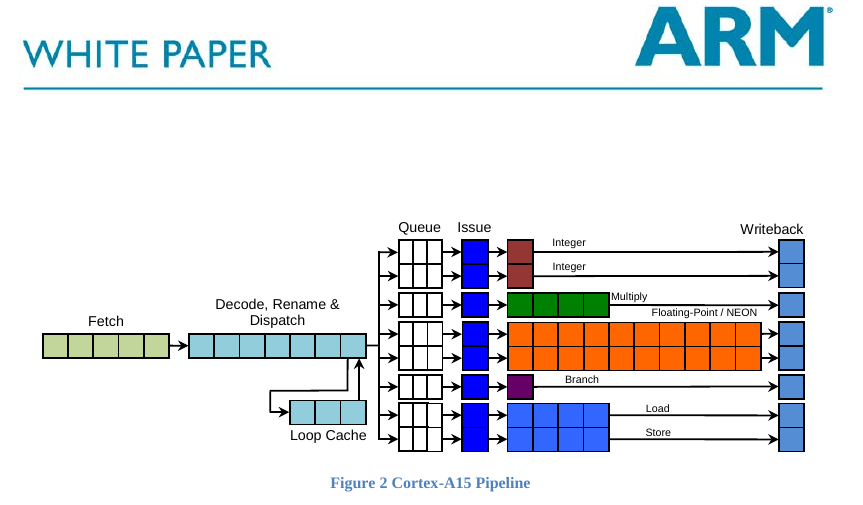

Da ARMs erster big.LITTLE so oft zitiert wird, lohnt es sich durchaus in deren Whitepaper von 2011 zum ersten SoC mit dieser Implementierung hineinzuschauen. Die Kerne waren schon arg unterschiedlich, beherrschten aber beide vollständig den ARM v7A Befehlssatz.

Es wird also durchaus berechtigweise angemerkt, dass AMDs Lösung nicht der Implementierung von ARM folgt und demnach auch semantisch nicht big.LITTLE entspricht.

-> https://web.archive.org/web/20120417183714/http://www.arm.com/files/downloads/big.LITTLE_Final.pdf

Es wird also durchaus berechtigweise angemerkt, dass AMDs Lösung nicht der Implementierung von ARM folgt und demnach auch semantisch nicht big.LITTLE entspricht.

-> https://web.archive.org/web/20120417183714/http://www.arm.com/files/downloads/big.LITTLE_Final.pdf

Zuletzt bearbeitet:

Das kann doch aber eh nicht zutreffen, weil "big.LITTLE" ein Markenzeichen von ARM ist - und das ganze auch entsprechend nur so zu verwenden ist, wie es ARM gern möchte?4nanai schrieb:Es wird also durchaus berechtigweise angemerkt, dass AMDs Lösung nicht der Implementierung von ARM folgt und demnach auch semantisch nicht big.LITTLE entspricht.

-> https://web.archive.org/web/20120417183714/http://www.arm.com/files/downloads/big.LITTLE_Final.pdf

https://www.arm.com/company/policies/trademarks/arm-trademark-list/biglittle-trademark

Kein Plan in wie weit das rechtlich jetzt ein Problem ist - aber ich würde das ganze Konstrukt hier eher Big/Little Design oder Prinzip nennen anstatt den ARM Begriff dafür zu benutzen. Das macht nämlich weder Intel noch AMD wenn ich das richtig sehe.

Die Redaktionen wollen in aller Regel auch nicht big.LITTLE von ARM nennen, sondern doch eigentlich nur das grundlegende Prinzip unterschiedlicher Kern-Ausbauten in einem einzigen Prozessor.

Das trifft aber wenn man es darauf reduziert, auch auf die Intel wie auch AMD Umsetzung zu. Denn alle sind AMD64 kompatibel und beherschen intern alle aktiven Befehlserweiterungen. Ja auch AVX512 bei Intel ist kein Problem, denn die CPUs könnten es im Silizium, es ist aber hart deaktiviert via Microcode (mittlerweile). Damit ist das ganze auch Featuregleich...4nanai schrieb:Die Kerne waren schon arg unterschiedlich, beherrschten aber beide vollständig den ARM v7A Befehlssatz.

Gracemont ist wie auch die P-Cores Out of Order. Anders als frühere Atom Implementierungen. Und anders als der erste ARM Ansatz aus deinem Whitepaper.

Bei AMD logischerweise auch, da es sich Architektonisch nicht unterscheidet zwischen C und normal.

Zuletzt bearbeitet:

Da ich mir gerade ein Elitebook mit einem 7840U konfiguriert habe (wobei der Konfigurator im letzten Schritt gestorben ist 🤮 ): Der wird all-core mit 8x 3,3 GHz angegeben. Bei 4 nm geht mit dem Budget schon einiges - auch ohne abgespeckte 4c-Kerne.Ozmog schrieb:Ja, weil sie einen unterschiedlichen Maximaltakt haben. 3,5GHz vs 4,9GHz sind eben diese ca 30%

Wenn es um APUs für Notebooks mit einer TDP von 15-30W geht, kann man grob abschätzen, dass Allcore wohl nicht einmal die 3,5GHz ansatzweise gehalten werden können,

[...]

Wie gesagt, kann man bei einer U-CPU mit 6 Kernen eh nicht viel mit Turbo auf mehr als 2 Kernen anfangen. Es wird entscheidener, wie sich die Dense-Cores im Teillastbereich verhalten, also bei gleichen Takt auch weniger Leistung aufnehmen. Dann ist es sogar möglich, dass man mit den Dense-Cores sogar schneller ist, weil sie weniger Leistung benötigen und damit dann auch der Takt wieder höher angesetzt werden kann.

Vom Prinzip also insgesamt nicht das schlechteste Konzept, man hat weiterhin zwei schnelle Kerne, die im Boost bis 4,9 Ghz gehen, der dann eh nur bei Lasten auf 1-2 Cores kurz gehalten werden kann. Und der Rest ist mit den Dense-Cores ausgerüstet, sodass man weiterhin 6 Kerne voll nutzen kann.

[...]

Schon, nur ändert das nichts daran, dass ich - abgesehen von Speziellen Bereichen wie z.B. Smartphones - keinen Vorteil in den Hybrid-CPUs sehe.CDLABSRadonP... schrieb:Entsprechend sollte das jetzt auch abgeräumt sein, oder?

Die meisten Nutzer können einen 7950X (oder TR) gar nicht auslasten und Intel stopft nun immer mehr von den E-Kernen in die CPUs. IMHO völlig nutzlos und verzweifeltes "wir müssen in den theoretischen Benchmarks oben stehen". Dass AMD jetzt auch auf die Schiene geht...

Was glaubst Du bitte war Zen bei seiner Vorstellung, wenn nicht ein Versuch mit einem Haufen lahmer Kerne in davon spezifisch profitierenden Anwendungen konkurrenzfähig zu sein?Nagilum99 schrieb:Dass AMD jetzt auch auf die Schiene geht...

@4nanai

Danke für das Whitepaper, darum ging es mir im Prinzip, es ist eben in keinsterweise vergleichbar mit ARMs oder Intels lösung, es ist nicht eine "richtige" Heterogene µArchitektur

Es geht hier eher darum das man so AMD eben "unrecht" tut wenn man das mit ARM oder Intel vergleichen möchte.

Ich lese hier bspw. schon:

Der nächste nimmt es wieder ernst und sagt "ja ein Zen4c Kern ist ja nur ein Billigkern"

Grundsätzlich sind es die gleichen Kerne, nur durch eine Vorauswahl "weniger" bissig... als würde man sagen ich kann meinen Curveoptimizer halt nur für 6 von 8 Kernen verwenden weil AMD diese "lockt" oder ähnliches...

Ein Vergleich ist schwer weil es eben ein neuer Ansatz ist.

Vorteil ist bspw. das ein Scheduler gar nicht so hart zwischen den Kernen unterscheiden muss, weil die "Rohleistung" viel Enger zusammen liegt, damit wird AMD die Probleme von P/E Cores möglicherweise umgehen können, man könnte meinen die ganze CCD Show hat AMD geholfen um zu lernen

Danke für das Whitepaper, darum ging es mir im Prinzip, es ist eben in keinsterweise vergleichbar mit ARMs oder Intels lösung, es ist nicht eine "richtige" Heterogene µArchitektur

Es geht hier eher darum das man so AMD eben "unrecht" tut wenn man das mit ARM oder Intel vergleichen möchte.

Ich lese hier bspw. schon:

auch ohne abgespeckte 4c-Kerne.

Der nächste nimmt es wieder ernst und sagt "ja ein Zen4c Kern ist ja nur ein Billigkern"

Grundsätzlich sind es die gleichen Kerne, nur durch eine Vorauswahl "weniger" bissig... als würde man sagen ich kann meinen Curveoptimizer halt nur für 6 von 8 Kernen verwenden weil AMD diese "lockt" oder ähnliches...

Ein Vergleich ist schwer weil es eben ein neuer Ansatz ist.

Vorteil ist bspw. das ein Scheduler gar nicht so hart zwischen den Kernen unterscheiden muss, weil die "Rohleistung" viel Enger zusammen liegt, damit wird AMD die Probleme von P/E Cores möglicherweise umgehen können, man könnte meinen die ganze CCD Show hat AMD geholfen um zu lernen

naja dann scheine ich echt wohl ne ausnahme zu sein das ich selbst nen 7950x voll auslasten kann.

Mir war nicht klar gewesen das es doch einen IPC steigerung von 8 % gegenüber Zen 3 gegeben hatte.Scheinbar sind die 13 % IPC Steigerung nur Theoretischer Wert.

Wenn da AMD noch mehr Optimierung reinsteckt geht viellicht sogar noch mehr auch ohne den Allcore Takt zu erhöhen.

Dann sehe ich da am Ende villeicht sogar noch mehr Steigerung.

Einer konnte sogar den 7950x3d dazu bringen niedrigere Taktraten zu leisten.Meinte das mit 3,9 ghz Allcore Takt der 7950x locker auch in kleine Geräte packen kann ohne viel Strom zu fressen oder auch Temperatur Probleme zu haben.Das nach oben nichts mehr ging als bis maximal 5,5 ghz hatte er kurz mal ausprobiert gehabt.

Im Grunde genommen geht also auch mehr Kerne mit bis 4 ghz bei 80 Watt ohne Probleme.Man sieht also der Takt macht das meiste davon aus.Ich finde es gut zu wissen das auch so Leistung auf der Straße kommt.

Gemessen wurde also bei rund 4 ghz Allcore.Ich mit meinem 5950x bei 3, ghz vs 7950x3d mit 3,9 ghz Allcore Takt.

Es dauert zwar dann länger um immer mehr Leistung zu haben,aber gehen tut es sehr wohl.

Mir war nicht klar gewesen das es doch einen IPC steigerung von 8 % gegenüber Zen 3 gegeben hatte.Scheinbar sind die 13 % IPC Steigerung nur Theoretischer Wert.

Wenn da AMD noch mehr Optimierung reinsteckt geht viellicht sogar noch mehr auch ohne den Allcore Takt zu erhöhen.

Dann sehe ich da am Ende villeicht sogar noch mehr Steigerung.

Einer konnte sogar den 7950x3d dazu bringen niedrigere Taktraten zu leisten.Meinte das mit 3,9 ghz Allcore Takt der 7950x locker auch in kleine Geräte packen kann ohne viel Strom zu fressen oder auch Temperatur Probleme zu haben.Das nach oben nichts mehr ging als bis maximal 5,5 ghz hatte er kurz mal ausprobiert gehabt.

Im Grunde genommen geht also auch mehr Kerne mit bis 4 ghz bei 80 Watt ohne Probleme.Man sieht also der Takt macht das meiste davon aus.Ich finde es gut zu wissen das auch so Leistung auf der Straße kommt.

Gemessen wurde also bei rund 4 ghz Allcore.Ich mit meinem 5950x bei 3, ghz vs 7950x3d mit 3,9 ghz Allcore Takt.

Es dauert zwar dann länger um immer mehr Leistung zu haben,aber gehen tut es sehr wohl.

Noch Mal kurz meine Sicht zu dem unsäglichen Hick Hack mit big.LITTLE, AMD und Intel.

Hybrid CPUs wurden von Arm eingeführt und Arm hat sich die Bezeichnung big.LITTLE schützen lassen.

Arm ging es darum die Laufzeit von Mobilgeräten zu optimieren, indem Task die wenig Performance benötigen auf Kernen laufen die auf maximale Effizienz getrimmt sind. Bei Mobiltelefonen ist dies extrem wichtig weil diese immer aktiv sind.

Intel hatte das Problem, dass sie nicht mit der Anzahl der Kerne bei AMD mithalten konnte. Intel hat sich deswegen von Arm inspirieren lassen und ging eigene Wege. Es ist Intel damit gelungen die Multi-Thread-Performance zu erhöhen und seinerseits AMD auf dem Desktop in Bedrägnis zu bringen.

Auch bei Intel sind die E-Cores nur bei kleinen Frequenzen effizienter als die P-Cores. AFAIK betreibt Intel die E-Cores aber mit einer höheren Taktfrequenz und somit sind diese nicht effizienter als die P-Cores. Sie sind kompakter und ermöglichen es aus der selben Die-Fläche mehr Multi-Thread-Performance herauszuholen.

Der größte Kritikpunkt an Intels bisheriger Lösung ist, dass Intel AVX-512 und den P-Cores deaktivieren musste, obwohl diese Funktion mit einem erheblichen Flächenaufwand implementiert wurde. Dies will Intel in Zukunft mit AVX-10 beheben.

Die E-Cores bei Intel sind deshalb so klein, weil der L2-cache aus ihnen herausgelöst wurde und 4 Cores sich den L2-Cache teilen. AMD hat bei Zen 4c den L2-Cache im Kern belassen und dieser macht ca 40 % der Fläche eines Kerns aus.

AMD hat Zen 4c für die Anforderungen der Cloudanbieter entwickelt. Diese benötigen keine hohe Single Thread Leistung aber möglichst viele Threads (Je Kern eine Anwendung). Bergamo macht aber auch bei Multithreads-Applikationen (Eine Anwendung auf vielen Threads) eine gute Figur.

Zen 4c wird auch in Hybrid-APUs (Phoenix 2) mit kleinem PowerBudget (15 W) eine gute Figur machen. Bei 28 W ist man IMO mit einer Phonix APU besser dran. Bei mehr Power ergibt es keinen Sinn beim Client Zen 4c Kerne anzubieten.

Eine weitere Anwendung von Zen 4c wird bei Siena bei kleinen, effizienten Servern kommen. Ob es hier für Hybridlösungen einen Markt gibt, kann ich nicht beurteilen.

Was der Impakt ist werden wir sehen.

Es gibt verschiedene Methoden um kompaktere Kerne zu realisieren. Aus dem Die Shot kann man bestimmen, dass der L2-Cache 40 % der Fläche einnimmt. Ich frage mich, ob dieses massive Fläche-Investment bei einem E-Cores tatsächlich sinnvoll ist.

Es gibt ein umstrittenes Leak das angeblich Sreenshots von HWInfo mit Engineering Sample von Strix Point zeigt. Es ist umstritten weil die Angaben teils unsinnig und auch zwischen den Screen unterschiedlich (L3-Cache) sind. Der eine Scree zeigt dass 4 E-Cores über einen gemeinsamen L2-Cache gekoppelt sind und dass E und P Cores einen gemeinsamen cache von 8 GByte haben.

Ich als Laie halte es für eine sinnvolle Optimierung, wenn sich mehrere E-Cores den L2-Cache teilen. Zumindest bei den Hybrid-APUs.

Diese ganze Diskussion dass bei AMD beide Kerne dieselbe IPC haben und bei Intel nicht, könnte sich bei Zen 5 in Luft auflösen. Auf was es ankommt ist, dass die Kerne einer Hybrid-CPU dieselbe ISA haben. Wie man an der unterschiedlichen Umsetzungen von AVX-512 bei AMD und Intel sieht, kann man dieselben Befehle unterschiedlich implementieren. Das wirkt sich auf den Flächenverbrauch und auf die IPC aus.

AMD musste bei Zen 4c das RTL (Register Transfer Language, Programmiersprache in der die Funktion von Chips definiert wird) von Zen 4 nehmen und neu designen. Für Zen 4c noch Mal das RTL von zen 4 anzupassen hätte zu viel Zeit gekostet. Bei Zen 5 hatte AMD mehr Zeit und deswegen ist es möglich, dass sich Zen 5 und Zen 5c auch im RTL unterscheiden. Also dass AMD die Kerne schon auf dieser Ebene für die jeweiligen Anwendungsfelder optimiert hat.

Gerade im Embedded Bereich gibt es für kleine und effiziente Kerne viele potentielle Anwendungen. Ich weiß aber nicht, ob dort tatsächlich noch jemand X86 haben möchte. Als Intel Altera übernommen hat, gab es sofort Spekulationen über Produkte die X86 mit FPGAs koppeln. Es gibt sie bis heute nicht. Auch bei der Übernahme von Xilinx gab es wieder diese Spekulationen.

Ein kritischer Punkt bei Hybrid CPUs ist immer die Verteilung der Last. Threads, die viel Perfomance benötigen müssen auf die P-Kerne und Threads die wenig Performance benötigen müssen auf die E-Kerne. Üblicherweise ist dies Verteilung der Threads die Aufgabe der Scheduler des Betriebssystems. Es bleibt abzuwarten wie sich dies entwickelt. Intel hatte bei Alder Lake keine Zeit auf die Betriebssysteme zu warten und hat mit dem Thread Director einen eigenen Scheduler On Die realisiert. Es wäre nicht das erste Mal dass sich herausstellt, das Hardware viel effizienter und flexibler als Software ist. Es könnte sein dass AMD auch bei Scheduling nachziehen muss.

Eine weitere Herausforderung sind lang laufende Threads, die in verschiedene Phasen unterschiedlich Performance benötigen. Hier wäre es ideal sie je nach aktuellem Bedarf zwischen den E- und P-Cores zu verschieben.

Wie viele verschiedene Kerne der bietet Arm derzeit aktuell an.?

Wie viele unterschiedliche Designs dieser Kerne gibt es? Von Arm? Von den Kunden?

Ich weiß nur dass die Zahlen groß sind.

Als Arm big.Little eingeführt hat, konnte sich Arm aus einer sehr großen Auswahl an Kernen bedienen. Für jeden Node gibt es sehr viele Kerne zur Auswahl. Natürlich hat Arm unterschiedliche Kerne ausgewählt, weil sie damit den größten Effekt erzielen konnten.

AMD hat viel weniger Kerne zur Auswahl. Zen und Zen+ auf GF 14 nm, Zen 2 und Zen 3 auf TSMC 7 nm und Zen 4 und Zen 4c auf TSMC 5 nm.

Also kann AMD momentan nur eine Hybrid-CPU aus Zen 4 und Zen 4c bauen. AMD konnte bei Phoenix 2 gar nicht anders vorgehen. Und bei Zen 5 kommt es eben darauf an was AMD für die Nachfolger von Bergamo und Siena benötigt. Wenn es hier besser ist ebenso wie bei Zen 4c vorzugehen, wird Zen 5c auch wieder nur ein anderes Design von Zen 5 sein. Aber es kann eben auch anders kommen.

Und bei Arm werden in den meisten aktuellen Desings 3 unterschiedliche Kerne verwendet.

Ich hoffe es gibt bald Benchmarks zu 7540U und 7640U. Vor allem getrennt für 15 W und für 28 W.

Wie sich Zen 5c zu Zen 5 verhält werden wir erst noch sehen. Aber nach dem was sich nach diesem ersten Test abzeichnet, sehe ich die für Strix genannte Konfiguration 4 + 8 kritisch.

Hybrid CPUs wurden von Arm eingeführt und Arm hat sich die Bezeichnung big.LITTLE schützen lassen.

Arm ging es darum die Laufzeit von Mobilgeräten zu optimieren, indem Task die wenig Performance benötigen auf Kernen laufen die auf maximale Effizienz getrimmt sind. Bei Mobiltelefonen ist dies extrem wichtig weil diese immer aktiv sind.

Intel hatte das Problem, dass sie nicht mit der Anzahl der Kerne bei AMD mithalten konnte. Intel hat sich deswegen von Arm inspirieren lassen und ging eigene Wege. Es ist Intel damit gelungen die Multi-Thread-Performance zu erhöhen und seinerseits AMD auf dem Desktop in Bedrägnis zu bringen.

Auch bei Intel sind die E-Cores nur bei kleinen Frequenzen effizienter als die P-Cores. AFAIK betreibt Intel die E-Cores aber mit einer höheren Taktfrequenz und somit sind diese nicht effizienter als die P-Cores. Sie sind kompakter und ermöglichen es aus der selben Die-Fläche mehr Multi-Thread-Performance herauszuholen.

Der größte Kritikpunkt an Intels bisheriger Lösung ist, dass Intel AVX-512 und den P-Cores deaktivieren musste, obwohl diese Funktion mit einem erheblichen Flächenaufwand implementiert wurde. Dies will Intel in Zukunft mit AVX-10 beheben.

Die E-Cores bei Intel sind deshalb so klein, weil der L2-cache aus ihnen herausgelöst wurde und 4 Cores sich den L2-Cache teilen. AMD hat bei Zen 4c den L2-Cache im Kern belassen und dieser macht ca 40 % der Fläche eines Kerns aus.

AMD hat Zen 4c für die Anforderungen der Cloudanbieter entwickelt. Diese benötigen keine hohe Single Thread Leistung aber möglichst viele Threads (Je Kern eine Anwendung). Bergamo macht aber auch bei Multithreads-Applikationen (Eine Anwendung auf vielen Threads) eine gute Figur.

Zen 4c wird auch in Hybrid-APUs (Phoenix 2) mit kleinem PowerBudget (15 W) eine gute Figur machen. Bei 28 W ist man IMO mit einer Phonix APU besser dran. Bei mehr Power ergibt es keinen Sinn beim Client Zen 4c Kerne anzubieten.

Eine weitere Anwendung von Zen 4c wird bei Siena bei kleinen, effizienten Servern kommen. Ob es hier für Hybridlösungen einen Markt gibt, kann ich nicht beurteilen.

Du spielst auf FinFlex an. Was hier neu ist, dass unterschiedliche Zellbibliotheken im selben Block gemischt werden können und dass eine 3. Zellbibliothek hinzu kommt.RKCPU schrieb:TSMC wird ja ab 3nm die Möglichkeit anbieten für .little CPU's effizientere Transistoren auf dem gleichen DIE zu .big anzubringen.

Was der Impakt ist werden wir sehen.

Es ist die Frage ob AMD bei Strix Point tatsächlich auf 3 nm wechselt. APUs haben haben sehr viel IO auf dem Chip die praktisch nicht nicht skaliert. Bei den Leaks deutet sehr viel darauf hin dass AMD bei Strix Point auf 4 nm bleibt.RKCPU schrieb:Daher sind E-Cores mit SMT und gleicher IPC zu großen Cores für Multicore mit engen TDP / Watt-optimiert ein gutes Konzept.

Ab Zen5 will AMD ja 2:1 Zen5c bringen, wie 8x Zen5c zu 4x Zen5.

Es gibt verschiedene Methoden um kompaktere Kerne zu realisieren. Aus dem Die Shot kann man bestimmen, dass der L2-Cache 40 % der Fläche einnimmt. Ich frage mich, ob dieses massive Fläche-Investment bei einem E-Cores tatsächlich sinnvoll ist.

Es gibt ein umstrittenes Leak das angeblich Sreenshots von HWInfo mit Engineering Sample von Strix Point zeigt. Es ist umstritten weil die Angaben teils unsinnig und auch zwischen den Screen unterschiedlich (L3-Cache) sind. Der eine Scree zeigt dass 4 E-Cores über einen gemeinsamen L2-Cache gekoppelt sind und dass E und P Cores einen gemeinsamen cache von 8 GByte haben.

Ich als Laie halte es für eine sinnvolle Optimierung, wenn sich mehrere E-Cores den L2-Cache teilen. Zumindest bei den Hybrid-APUs.

Diese ganze Diskussion dass bei AMD beide Kerne dieselbe IPC haben und bei Intel nicht, könnte sich bei Zen 5 in Luft auflösen. Auf was es ankommt ist, dass die Kerne einer Hybrid-CPU dieselbe ISA haben. Wie man an der unterschiedlichen Umsetzungen von AVX-512 bei AMD und Intel sieht, kann man dieselben Befehle unterschiedlich implementieren. Das wirkt sich auf den Flächenverbrauch und auf die IPC aus.

AMD musste bei Zen 4c das RTL (Register Transfer Language, Programmiersprache in der die Funktion von Chips definiert wird) von Zen 4 nehmen und neu designen. Für Zen 4c noch Mal das RTL von zen 4 anzupassen hätte zu viel Zeit gekostet. Bei Zen 5 hatte AMD mehr Zeit und deswegen ist es möglich, dass sich Zen 5 und Zen 5c auch im RTL unterscheiden. Also dass AMD die Kerne schon auf dieser Ebene für die jeweiligen Anwendungsfelder optimiert hat.

Es gibt auch viele andere Anwendungsgebiete für Zen 4c und seine Nachfolger.RKCPU schrieb:Mittelfristig dürften auch Thin Clients so besser bestückt sein als mit großen Cores.

Gerade im Embedded Bereich gibt es für kleine und effiziente Kerne viele potentielle Anwendungen. Ich weiß aber nicht, ob dort tatsächlich noch jemand X86 haben möchte. Als Intel Altera übernommen hat, gab es sofort Spekulationen über Produkte die X86 mit FPGAs koppeln. Es gibt sie bis heute nicht. Auch bei der Übernahme von Xilinx gab es wieder diese Spekulationen.

Die Frage ist ganz alleine, mit welcher Taktfreqenz Sony die CPU betreiben will. Wenn sie in einem Frequenz-Bereich läuft bei dem Zen 4c Vorteile hat, wird Sony Zen 4c verwenden. Ich denke nicht dass Sony den Programmierern eine Hybrid-APU zumuten wird.RKCPU schrieb:Auch Konsolen dürften sich so entwickeln, eine PS5 pro mit 4x Zen4 plus 4x Zen4c z.B. Die normale PS5 könnte dann bei 8x Zen4c bleiben.

Ein kritischer Punkt bei Hybrid CPUs ist immer die Verteilung der Last. Threads, die viel Perfomance benötigen müssen auf die P-Kerne und Threads die wenig Performance benötigen müssen auf die E-Kerne. Üblicherweise ist dies Verteilung der Threads die Aufgabe der Scheduler des Betriebssystems. Es bleibt abzuwarten wie sich dies entwickelt. Intel hatte bei Alder Lake keine Zeit auf die Betriebssysteme zu warten und hat mit dem Thread Director einen eigenen Scheduler On Die realisiert. Es wäre nicht das erste Mal dass sich herausstellt, das Hardware viel effizienter und flexibler als Software ist. Es könnte sein dass AMD auch bei Scheduling nachziehen muss.

Eine weitere Herausforderung sind lang laufende Threads, die in verschiedene Phasen unterschiedlich Performance benötigen. Hier wäre es ideal sie je nach aktuellem Bedarf zwischen den E- und P-Cores zu verschieben.

Und genau darauf kommt es an. Kerne mit unterschiedliche ISA in einer CPU zu verwenden führt unweigerlich zu Komplikationen.4nanai schrieb:Die Kerne waren schon arg unterschiedlich, beherrschten aber beide vollständig den ARM v7A Befehlssatz.

Diese Argumentation führt zu nichts.4nanai schrieb:Es wird also durchaus berechtigweise angemerkt, dass AMDs Lösung nicht der Implementierung von ARM folgt und demnach auch semantisch nicht big.LITTLE entspricht.

Wie viele verschiedene Kerne der bietet Arm derzeit aktuell an.?

Wie viele unterschiedliche Designs dieser Kerne gibt es? Von Arm? Von den Kunden?

Ich weiß nur dass die Zahlen groß sind.

Als Arm big.Little eingeführt hat, konnte sich Arm aus einer sehr großen Auswahl an Kernen bedienen. Für jeden Node gibt es sehr viele Kerne zur Auswahl. Natürlich hat Arm unterschiedliche Kerne ausgewählt, weil sie damit den größten Effekt erzielen konnten.

AMD hat viel weniger Kerne zur Auswahl. Zen und Zen+ auf GF 14 nm, Zen 2 und Zen 3 auf TSMC 7 nm und Zen 4 und Zen 4c auf TSMC 5 nm.

Also kann AMD momentan nur eine Hybrid-CPU aus Zen 4 und Zen 4c bauen. AMD konnte bei Phoenix 2 gar nicht anders vorgehen. Und bei Zen 5 kommt es eben darauf an was AMD für die Nachfolger von Bergamo und Siena benötigt. Wenn es hier besser ist ebenso wie bei Zen 4c vorzugehen, wird Zen 5c auch wieder nur ein anderes Design von Zen 5 sein. Aber es kann eben auch anders kommen.

Die TradeMark freie Bezeichnung ist Hybrid CPU.fdsonne schrieb:Kein Plan in wie weit das rechtlich jetzt ein Problem ist - aber ich würde das ganze Konstrukt hier eher Big/Little Design oder Prinzip nennen anstatt den ARM Begriff dafür zu benutzen. Das macht nämlich weder Intel noch AMD wenn ich das richtig sehe.

Und bei Arm werden in den meisten aktuellen Desings 3 unterschiedliche Kerne verwendet.

In der Tendenz stimme ich Dir zu. Ich erwarte allenfalls bei 15 W oder weniger und Akkubetrieb einen Nutzen, ...Nagilum99 schrieb:Da ich mir gerade ein Elitebook mit einem 7840U konfiguriert habe (wobei der Konfigurator im letzten Schritt gestorben ist 🤮 ): Der wird all-core mit 8x 3,3 GHz angegeben. Bei 4 nm geht mit dem Budget schon einiges - auch ohne abgespeckte 4c-Kerne.

Ich hoffe es gibt bald Benchmarks zu 7540U und 7640U. Vor allem getrennt für 15 W und für 28 W.

Ich gebe Dir recht, dass es bei Phonix 2 eng wird. Vor allem weil X86 bei den Geräteklassen bei denen diese CPU glänzen könnte keine Rolle mehr spielt.Nagilum99 schrieb:Schon, nur ändert das nichts daran, dass ich - abgesehen von Speziellen Bereichen wie z.B. Smartphones - keinen Vorteil in den Hybrid-CPUs sehe.

Es gibt keine Anzeichen, dass AMD Zen 4c im Desktop anbieten wird.Nagilum99 schrieb:Dass AMD jetzt auch auf die Schiene geht...

Wie sich Zen 5c zu Zen 5 verhält werden wir erst noch sehen. Aber nach dem was sich nach diesem ersten Test abzeichnet, sehe ich die für Strix genannte Konfiguration 4 + 8 kritisch.

Das mag da stehen, aber es gibt doch von AMD keine Zusage zu einem fixen Allcore Boost Takt, da dieser von der Temperatur/dem Kühlsystem, dem Workload und anderen Faktoren abhängig ist.Nagilum99 schrieb:Da ich mir gerade ein Elitebook mit einem 7840U konfiguriert habe (wobei der Konfigurator im letzten Schritt gestorben ist 🤮 ): Der wird all-core mit 8x 3,3 GHz angegeben. Bei 4 nm geht mit dem Budget schon einiges - auch ohne abgespeckte 4c-Kerne.

Mein 6850U Pro in eben so einem Elitebook G9 Gerätli erreicht mit vier Threads Prime95 non AVX auf vier von acht Kernen 25W Leistungsaufnahme und damit das Powerlimit. Die vier Kerne takten dabei bei ca. 3,2GHz und das Teil wird fast 100°C warm. Sicher kann es der neuere Prozess etwas besser - aber da sind keine 100% Effizienzsteigerung zu verbuchen. Never ever...

Bei 8 Threads auf 8 Kerne ohne SMT sind es ca. 2,5-2,6GHz, 25W und ähnlich hohe Temperaturen.

Was über bleibt wenn man das jetzt mit C-Cores verarztet ist schlicht die Flächeneinsparung im Silizum.

Der Vorteil ist die Flächeneinsparung, was gerade im Einsteigerbereich für den Hersteller Punkte bringt, weil es eben weniger unnötig teuer produzierte Waferfläche benötigt.Nagilum99 schrieb:Schon, nur ändert das nichts daran, dass ich - abgesehen von Speziellen Bereichen wie z.B. Smartphones - keinen Vorteil in den Hybrid-CPUs sehe.

Ist er doch auch?PUNK2018 schrieb:Der nächste nimmt es wieder ernst und sagt "ja ein Zen4c Kern ist ja nur ein Billigkern"

Die Frage ist, wie definiert man "billig" in dem Fall?

Ein C Core wird nie so hoch takten können wie ein vollwertiger Zen Core.

Das ist weniger das Problem. Vor allem in Benchmarks, wo eh nichts außer der Benchmark läuft.PUNK2018 schrieb:Vorteil ist bspw. das ein Scheduler gar nicht so hart zwischen den Kernen unterscheiden muss, weil die "Rohleistung" viel Enger zusammen liegt, damit wird AMD die Probleme von P/E Cores möglicherweise umgehen können, man könnte meinen die ganze CCD Show hat AMD geholfen um zu lernen

Ich sehe die Herausforderung eher im Alltag, wo man entweder über Handoptimierung (siehe X3D CPUs mit der Gamebar) oder Randombox agiert. Der Scheduler kann nicht von extern wissen, was jetzt vom Workload wichtig ist und was nicht. Er kann auch nicht mitdenken oder ähnliches. Um so höher die Load, desto problematischer wird das, wenn im Workload Laufzeitkritisches dabei ist. Abseits von generischem MT Volllastkram, wo es praktisch irrelevant ist, wie lang ein einzelner Thread läuft, ist das im Alltag halt das größte Problem solcher Techniken.

Aber das hat/hätte es mit gleichen Kernen genau so, die verlieren halt Takt, damit läuft der Laufzeitkritische Kram auch langsamer als wenn die Kerne frei wären...

Auch SMT ist dabei ein großes Problem. Denn belegt ein zweiter Thread via SMT die Kern Ressourcen, verliert man am Ende fast 50% an Leistung, auch wenn die Summe beider Threads dann vielleicht mit 10, 20, 30% schneller agiert. Gaming + Rendern auf dem selben physischen Kern ist sozusagen eine ziemlich blöde Idee. Bekommt man dann mehr Kerne, bringt das in Summe auch Punkte, selbst wenn diese in total niedriger takten.

Wenn ich an Hybrid CPU denke, dann kommt mir als erstes AMDs Fusion in den Sinn. Nämlich ne GPU und ne CPU zu vereinen.ETI1120 schrieb:Die TradeMark freie Bezeichnung ist Hybrid CPU.

Unterschiedlich große/schnelle/dicke/whatever Kerne in einem Design aber? Aber natürlich, vom Wording her kann Hybrid natürlich alles sein. Big/Little als Verwendung von "Groß und Klein" find ich aber genau so passend und wäre genau so Trademark frei.

Das ist auch der angegebene Basistakt, nicht der allcore-boost.fdsonne schrieb:Das mag da stehen, aber es gibt doch von AMD keine Zusage zu einem fixen Allcore Boost Takt, da dieser von der Temperatur/dem Kühlsystem, dem Workload und anderen Faktoren abhängig ist.

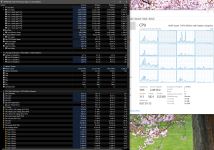

Deine Ergebnisse werfen Fragen auf. Mein aktuelles Elitebook G8 mit dem 5650U:Mein 6850U Pro in eben so einem Elitebook G9 Gerätli erreicht mit vier Threads Prime95 non AVX auf vier von acht Kernen 25W Leistungsaufnahme und damit das Powerlimit. Die vier Kerne takten dabei bei ca. 3,2GHz und das Teil wird fast 100°C warm. Sicher kann es der neuere Prozess etwas besser - aber da sind keine 100% Effizienzsteigerung zu verbuchen. Never ever...

Bei 8 Threads auf 8 Kerne ohne SMT sind es ca. 2,5-2,6GHz, 25W und ähnlich hohe Temperaturen.

Er packt zum Test irgendwas mit 7zip, sieht aber z.B. unter Veam oder LR ähnlich aus. Die iGPU erreicht dabei nur ~65 - 70 °C (das sollte mit etwas Laufzeit näherungsweise die CPU-Temperatur wiedergeben).

Den Vorteil akzeptiere ich - ob er nachher in Relation zurm Aufwand steht, wird sich zeigen.Der Vorteil ist die Flächeneinsparung, was gerade im Einsteigerbereich für den Hersteller Punkte bringt, weil es eben weniger unnötig teuer produzierte Waferfläche benötigt.

Sunjy Kamikaze

Commodore

- Registriert

- Aug. 2015

- Beiträge

- 4.577

Haben die dann USB 4.2 endlich im Chip drin? Ich will endlich mit eGPUs arbeiten können

Bei 30W wahrscheinlich. Bei mir steht da 2,6GHz Baseclock auf der AMD Page - HP limitiert aber anstatt bei 28 oder 30W eben bei 25W im Elitebook. Das packt er dann nicht ganz. Die Temperatur tut ihr übriges dazu.Nagilum99 schrieb:Das ist auch der angegebene Basistakt, nicht der allcore-boost.

Kannste nicht für ernst nehmen, die Taktrate im Taskmanager.Nagilum99 schrieb:Deine Ergebnisse werfen Fragen auf. Mein aktuelles Elitebook G8 mit dem 5650U:

Anhang anzeigen 1397184

Er packt zum Test irgendwas mit 7zip, sieht aber z.B. unter Veam oder LR ähnlich aus. Die iGPU erreicht dabei nur ~65 - 70 °C (das sollte mit etwas Laufzeit näherungsweise die CPU-Temperatur wiedergeben).

Schau lieber via HWInfo.

Er setzt sogar nach einer gewissen Zeit dann auf 15W runter und dann sinkt die Last, die Temperatur und der Takt drastisch.

Ein sehr sehr interessantes Verhalten zeigt mein Book dabei sogar noch, wenn man es einfach mal ne Weile mit 8T beschäftigt.

Die Last sinkt, der Takt sinkt, die Leistungsaufnahme bleibt. Das wirkt für mich irgendwie komisch, weil eigentlich müsste die Last gleich (hoch) bleiben, also den Thread voll ausfahren.

Hast du das auch? Man sieht schön die abfallende Kurve im Taskmanager. Die Kiste wird auch bisschen zäh dabei, wie als würde es Throtteln, was es aber laut HWInfo zumindest temperaturseitig nicht tut.

Der Aufwand ist doch quasi gleich Null?Nagilum99 schrieb:Den Vorteil akzeptiere ich - ob er nachher in Relation zurm Aufwand steht, wird sich zeigen.

Wenn man den Flächenangaben glaubt, so ist das ne Einsparung in der Fläche von ca. 1/3tel in total. Das heißt, für AMD lässt sich alles bis einschließlich 2+4C wahlweise als voll aktivierter Hybrid Chip oder als teildeaktivierter, viel größerer 8C Phoenix Chip fertigen. Warum sollten sie das verschenken?

Ob du praktisch über den max. Takt der C-Cores hinaus kommt, ist gerade bei enger Power Limitation und mauen Kühlern wie bspw. den HP Books schon fraglich?

fdsonne schrieb:Warum nicht?

Der E-Core mit in etwa Skylake IPC ist halt auch nur ca. 1/4tel so groß, sodass man vier dieser Cores auf die Fläche eines P-Cores unter bringt. Das heißt, du bekommst 100% mehr Threads ggü. einem P-Core mit SMT. Oder anders ausgedrückt, 8x P-Cores bei gleichem Takt sind ca. 30-50% schneller als 8x E-Cores, benötigen aber 4x so viel Fläche. Die Leistungsdifferenz steigt natürlich bei steigendem Takt weiter an. ~4GHz auf den E-Cores vs. 5GHz+ auf den P-Cores, aber wir sind immernoch weit weg von Faktor 4, wie die Flächeneinsparung.

Am Ende kommt das in der effektiven Performance ca. auf ähnliches Niveau wie AMDs Zen4C "Abspeckung". Denn dort sinkt die Performance nicht ggü. dem Zen4 Core. Dafür spart man aber auch nur ca. 30% der Fläche und hat obenraus ein Taktlimit.

Ein E-Core only Intel Design könnte mit um die max. 4GHz also theoretisch ohne mehr Fläche auf 48C/48T kommen - analog einem 13900er. Das ist winzig wenn man das mal ggü. einem 48 Core Epyc vergleicht. Skaliert man das auf ein Maximum, so wäre bei den riesen Trümmern von AMD und Intel im Server Bereich da dicke mittlere 3-Stellige Core Anzahlen möglich, mit inkl. der entsprechenden Leistung bei Software die 1:1 skaliert.

Das kommt jetzt drauf an wie man sie konfigurieren kann. Die AMDs C Cores sparen zwar nicht extrem viel Fläche, aber man muss halt kucken, was bei 3 Ghz Takt an Effizienz übrig bleibt.

Bei der Skylake IPC für einen E Core, brauchst die 4 Ghz auch dringend, wenn man irgendwas reissen will.

Die IPC eines dieser Zen 4C Kerne dürfte etwa 35-40% über den E-Cores liegen, wenn ich mich nicht völlig verrechnet habe, das sind dann doch Welten. Und für kleine Lasten reichen dann 2-3 Ghz auch locker aus.

Laut dem CB Test bei Alder Lake braucht ein P Core um die 21 W pro Stück und ein E Core um die 5-6W.

Wenn ichs richtig im Kopf habe, war ja schon ein normaler Zen 3 bei nur 4-8W pro Kern. Daher war der ja auch effizienter bei jeder TDP Stufe als Alder in dem Test und deshalb sind die E-Cores bis auf den Flächenverbrauch ja auch eher so mäh.

https://www.computerbase.de/artikel...12900k-i7-12700k-i5-12600k-test.78382/seite-2

Kann mir jemand, der sich eher damit auskennt, mir die Verteilung der USB Ports erklären?

Auf dem die shot sieht man zweimal USB4/2x USB3 und 8x USB2. USB2 ist offensichttlich immer noch sehr nützlich, um Tastatur, Maus/Touchpad und Webcam anzuschließen. Sind diese jeweils für 1 Port gedacht? Ich frage gerade deshalb, weil der USB4 Teil kaum größer ist und gleich 2 Ports anbieten kann.

Auf der AMD Produktseite sind hingegen 2xUSB4, 2x USB3 und 4x USB2 angegeben, zumindest letzteres erscheint logisch. Also ich verstehe unter USB4/2x USB3 entweder einmal oder zweimal. Wie kommt es dann dennoch zu 2x USB4 und 2x USB3?

Alle Angaben, die sich zwischen 7840/7640 und 7540/7440 unterscheiden, deuten stark darauf hin, dass es sich hier um Phoenix und Phoenix2 handeln muss. Der die shot spricht auch sehr dafür, man beachte nur die Anzahl der PCIe lanes. 20 für Phoenix und 14 für Phoenix 2.

Darüber hinaus macht deine Aufteilung im Sinne des salvage Prinzips auch wenig Sinn. 7640 ist schon eine salvage Variante von Phoenix. Ein salvage vom salvage wäre eher mit dem Ryzen 5 5600X3D vergleichbar und dieser war nur stark eingeschränkt verfügbar. Während AMDs mobile APUs allgemein besser verfügbar sein könnten... Es spricht also für:

7840 - full Phoenix ; 7640 - salvage of 7840

7540 - full Phoenix2 ; 7440 - salvage of 7540

Sollte es nicht exakt so sein, werde ich mich korrigieren.

Beim Zen4c kann man das wenigstens relativ leicht ermitteln (OK, sollte bei Intel genau so einfach sein). Typische Benchmarks haben in der Hinsicht den Nachteil, dass Zen4 die Arbeit schneller erledigen könnte und allein dadurch vielleicht effizienter insgesamt ist. Aber bei Spiele geht das ja nicht. Man müsste ein Spiel nehmen, das eine sehr hohe CPU-Anforderung hat und die GPU Bedingungen auf das absolute Minimum setzen (720p FSR Performance!). Welches läuft besser bzw. effizienter? Selbst wenn es gleich laufen würde, wäre das ein Pluspunkt für Zen4c, weil man diese APUs günstiger verkaufen kann (sofern der GPU Anteil ausreichen stark ist).

Auf dem die shot sieht man zweimal USB4/2x USB3 und 8x USB2. USB2 ist offensichttlich immer noch sehr nützlich, um Tastatur, Maus/Touchpad und Webcam anzuschließen. Sind diese jeweils für 1 Port gedacht? Ich frage gerade deshalb, weil der USB4 Teil kaum größer ist und gleich 2 Ports anbieten kann.

Auf der AMD Produktseite sind hingegen 2xUSB4, 2x USB3 und 4x USB2 angegeben, zumindest letzteres erscheint logisch. Also ich verstehe unter USB4/2x USB3 entweder einmal oder zweimal. Wie kommt es dann dennoch zu 2x USB4 und 2x USB3?

Und das bezweifle ich stark! Aber ich habe auch Argumente dafür. Du kannst dich nur auf die (wahrscheinlich) falsche Angabe der Chipgröße auf AMDs Website berufen.Alesis schrieb:Es ist ein Phoenix 7640, der um die Grafikeinheit beschnitten wurde.

Alle Angaben, die sich zwischen 7840/7640 und 7540/7440 unterscheiden, deuten stark darauf hin, dass es sich hier um Phoenix und Phoenix2 handeln muss. Der die shot spricht auch sehr dafür, man beachte nur die Anzahl der PCIe lanes. 20 für Phoenix und 14 für Phoenix 2.

Darüber hinaus macht deine Aufteilung im Sinne des salvage Prinzips auch wenig Sinn. 7640 ist schon eine salvage Variante von Phoenix. Ein salvage vom salvage wäre eher mit dem Ryzen 5 5600X3D vergleichbar und dieser war nur stark eingeschränkt verfügbar. Während AMDs mobile APUs allgemein besser verfügbar sein könnten... Es spricht also für:

7840 - full Phoenix ; 7640 - salvage of 7840

7540 - full Phoenix2 ; 7440 - salvage of 7540

Sollte es nicht exakt so sein, werde ich mich korrigieren.

Ich würde sogar von (deutlich) mehr als nur 2 ausgehen, aber man muss auch sagen, dass der Vergleich sehr schwierig. Aktuelle Software läuft so alter Hardware kaum bis gar nicht und die alte Software ist nicht für heutige Architekturen ausgelegt/optimiert - insbesondere hinsichtlich der Befehlserweiterungen.fdsonne schrieb:Allein der IPC Zuwachs bewegt sich in Größenordnung Faktor 2

Für deinen Einsatzzweck würde sich, ehrlich gesagt, sogar ein Smartphone SoC rentieren.JohnWickzer schrieb:Sowas als 6+6, meinetwegen auch 4+4, wäre doch für Media Server optimal, oder?

Nur Fileserver, Downloads. Kein Transcoding, Encoding oder sonstige Spielereien.

Das hat absolut nichts mit der AVX512 Thematik zu tun! Du hast den Zweck von Zen4c nicht verstanden, also bitte nochmal reinlesen.Fallout667 schrieb:Naja also die 4c Kerne takten ja auch nur mit 3,5 GHz, so ganz scheint AMD das Taktproblem auch nicht gelöst zu haben. Bzw wie viel Sinn macht AVX512 auf den kleinen Kernen bei so geringem Takt?

Muss sich ja erst noch zeigen. Bei Intels Variante hat sich gezeigt (sofern sich das nicht geändert hat), dass in einem P/E die die E-Cores eher hinderlich sind. Da wüsste ich gerne, wie sich eine Core xxxU CPU in der Hinsicht gibt.ETI1120 schrieb:Ich gebe Dir recht, dass es bei Phonix 2 eng wird. Vor allem weil X86 bei den Geräteklassen bei denen diese CPU glänzen könnte keine Rolle mehr spielt.

Beim Zen4c kann man das wenigstens relativ leicht ermitteln (OK, sollte bei Intel genau so einfach sein). Typische Benchmarks haben in der Hinsicht den Nachteil, dass Zen4 die Arbeit schneller erledigen könnte und allein dadurch vielleicht effizienter insgesamt ist. Aber bei Spiele geht das ja nicht. Man müsste ein Spiel nehmen, das eine sehr hohe CPU-Anforderung hat und die GPU Bedingungen auf das absolute Minimum setzen (720p FSR Performance!). Welches läuft besser bzw. effizienter? Selbst wenn es gleich laufen würde, wäre das ein Pluspunkt für Zen4c, weil man diese APUs günstiger verkaufen kann (sofern der GPU Anteil ausreichen stark ist).

Leider nein. Ist USB 4v2 überhaupt schon fertig spezifiziert? Das wurde überhaupt erst dieses Jahr angekündigt. Es würde mich wundern, wenn selbst nächstes Jahr schon Designs mit USB 4v2 angekündigt würden.Sunjy Kamikaze schrieb:Haben die dann USB 4.2 endlich im Chip drin? Ich will endlich mit eGPUs arbeiten können

Das lese ich immer wieder - aber woher nehmt ihr das denn immer?modena.ch schrieb:Bei der Skylake IPC für einen E Core, brauchst die 4 Ghz auch dringend, wenn man irgendwas reissen will.

So ein 8C P-Core Ding mit 5+GHz säuft halt auch über 200W.

Das kommt ja nicht von ungefähr... Wenn du 4x so viele Cores/doppelt so viele Threads auf die gleiche Fläche bekommst, kann man es sich ja erlauben für MT Lasten entsprechend niedriger und damit effizienter zu takten.

Die Alternative wäre, 1/4tel der E-Core Anzahl in Form von mehr P-Cores zu nutzen - beim 12900er wären das dann 10x P-Cores. Beim 13900er 12x P-Cores. Bei gleichem Powerbudget ist davon auszugehen, dass die MT Performance nicht wirklich steigt, nur ein klein wenig, eben um den Faktor wie die Effizienz bei fallendem Takt zulegt, wenn man 50% mehr Kerne hätte. -> da muss dann halt der Takt runter.

Das mag sein - aber dafür sind es ja in der Anzahl immernoch mehr von diesen E-Cores bei Intel? Selbst wenn man das 1:1 vergleicht, was aufgrund der anderen Architektur vor allem beim MCM Konstrukt schwierig ist.modena.ch schrieb:Die IPC eines dieser Zen 4C Kerne dürfte etwa 35-40% über den E-Cores liegen, wenn ich mich nicht völlig verrechnet habe, das sind dann doch Welten. Und für kleine Lasten reichen dann 2-3 Ghz auch locker aus.

Die E-Cores sollen wahrscheinlich gar nicht so sehr unter niedriger Teillast Energie sparen, sondern eher unter hoher Last mehr MT Leistung generieren ohne dass die Leistungsaufnahme zu stark leidet.

Bei den "K" Modellen kommt erschwerend hinzu, dass mit über 200W eben festgelegte Bereich auch eher ineffizient ist. Hart auf 125W gelockt bspw. sieht das um Welten anders aus. Man verliert nicht sooo viel wenn man das so fährt. Der Nachteil schlägt primär dort zu buche, wo man Laufzeitkritisches mit MT Load kombiniert. Also Zocken + Rendern im Hintergrund -> das frisst FPS bei zu niedrigem Powerlimit.

Mein 5950X mit 5050MHz Boost benötigt 22-25W für den Kern. Je nach Load schwankt das bisschen. Die P-Cores bei Intel gehen bis über 30W bei entsprechend hohem Takt, wenn man ihm freien Lauf lässt.modena.ch schrieb:Wenn ichs richtig im Kopf habe, war ja schon ein normaler Zen 3 bei nur 4-8W pro Kern. Daher war der ja auch effizienter bei jeder TDP Stufe als Alder in dem Test und deshalb sind die E-Cores bis auf den Flächenverbrauch ja auch eher so mäh.

https://www.computerbase.de/artikel...12900k-i7-12700k-i5-12600k-test.78382/seite-2

Das geht aber eben auch andersrum - so ein 64C 225W limitierter Epyc kommt bei um die 90W für den Uncore Bereich auf rechnerisch um die 2W pro Kern. Das halt dann nur noch in 2 Komma GHz... Aber die Leistung steigt weit weniger als um Faktor, wie die Energieaufnahme suggeriert.

Hier setzt halt der C-Core an. Niedrig getaktet durch ein hohes Powerlimit kann man sich die Fläche halt auch sparen, weil es eh nie dazu kommt. Und wenn doch - es hat ein paar vollwertige Kerne, die boosten dann entsprechend hoch...

Entwicklungsaufwand, extra produktionslinien... du unterschätzt was das kostet.fdsonne schrieb:Bei 30W wahrscheinlich. Bei mir steht da 2,6GHz Baseclock auf der AMD Page - HP limitiert aber anstatt bei 28 oder 30W eben bei 25W im Elitebook. Das packt er dann nicht ganz. Die Temperatur tut ihr übriges dazu.

Kannste nicht für ernst nehmen, die Taktrate im Taskmanager.

Schau lieber via HWInfo.

Anhang anzeigen 1397222

Er setzt sogar nach einer gewissen Zeit dann auf 15W runter und dann sinkt die Last, die Temperatur und der Takt drastisch.

Ein sehr sehr interessantes Verhalten zeigt mein Book dabei sogar noch, wenn man es einfach mal ne Weile mit 8T beschäftigt.

Anhang anzeigen 1397225

Die Last sinkt, der Takt sinkt, die Leistungsaufnahme bleibt. Das wirkt für mich irgendwie komisch, weil eigentlich müsste die Last gleich (hoch) bleiben, also den Thread voll ausfahren.

Hast du das auch? Man sieht schön die abfallende Kurve im Taskmanager. Die Kiste wird auch bisschen zäh dabei, wie als würde es Throtteln, was es aber laut HWInfo zumindest temperaturseitig nicht tut.

Der Aufwand ist doch quasi gleich Null?

Zum Rest: Nein, ich kann keine solche Kurven bei meinem Notebook beobachten, der hält die Leistung auch recht gut auf Dauer. Schon mal die Firmware aktualisiert?

Ich hatte überlegt das G10 mit einem 7840HS zu konfigurieren, aber ich denke aus Effizienzgründen wird es wieder ein U werden. Die Mehrleistung ist doch überschaubar.

Kann man so nicht sagen,kommt auf die Art der Software also die Verwendete Software drauf an.Was ist alt?Ist eine 5 Jahre alte Software schon alt? Meine ist aus 2018 und hat noch immer ne Leistungssteigerung auch wenn sie von neuen Befehlserweiterungen nicht mehr Profitiert.Solange die neue CPU für mehr Leistung sorgt ist mir das vollkommen egal wie viele neue Befehlserweiterung noch kommen,von mir aus kommen 1000 neue Befehlserweiterung,es kommt nicht auf das drauf an.Deinorius schrieb:Ich würde sogar von (deutlich) mehr als nur 2 ausgehen, aber man muss auch sagen, dass der Vergleich sehr schwierig. Aktuelle Software läuft so alter Hardware kaum bis gar nicht und die alte Software ist nicht für heutige Architekturen ausgelegt/optimiert - insbesondere hinsichtlich der Befehlserweiterungen.

Aber irgendwann komme ich dennoch an das Limit.Wenn mit jeder CPU und wievielen Steigerung,das bleibt spannend.Irgendwann müsste ich wirklich am Limit sein.Gleiche Version der Software,selbe Einstellung und selbe Quellmatial beim Videoumwandeln.Mal sehen wie viele Generation ich noch brauche bis nix mehr geht.Denke mal Zen 7 oder Zen 8 könnte hier das Ende sein.

Ich werde ganz sicher gegen ne Schallmauer oder ne Unisichtbare Wand mal stoßen.Weil eines ist sicher ne unendliche Steigerung der Leistung kann es ja echt nicht geben,es sei denn die Hersteller finden ne unendliche Verbesserungen,dann ja.