Nun man hat da nicht nur mit den physikalischen Grenzen bei Silizium zu kämpfen. Was ich gehört habe, wird es bei reinem Silizium ab weniger als 20nm kritisch, weil dann die Isolationsschichten (für gewöhnlich SiO2) zu dünn ausfallen, sodass sich sogenannte "Leckströme" zu einem ernsthaften Problem entwickeln, da dann ein Großteil der Elektronen nicht auf der Leiterbahn fließen würde, die eigentlich für sie vorgesehen ist, sondern einfach munter quer durch den ganzen Chip fließen würden (bildlich ausgedrückt). Tunneleffekte spielen hierbei eine sehr große Rolle, je kleiner die Struktur wird, desto größer ist die Wahrscheinlichkeit, dass ein Elektron "einfach wegtunnelt".

Das ganze kann man noch in den Griff bekommen, indem man andere Materialien verwendet, aber auch diese Möglichkeiten werden irgendwann (nach derzeitigem Stand bei ca. 11nm) erschöpft sein.

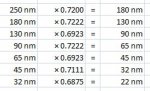

Bis dahin hat man aber auch noch mit anderen Problemen zu kämpfen, nämlich werden solche Chips ja per Laser belichtet und normalerweise schafft man nur Strukturen bis zu einer Größe der Wellenlänge des Lichts. Das lässt sich mit einigen Tricks umgehen (zur Zeit nutzt man Laserquellen mit 120-130nm), aber auch da müssen in sehr naher Zukunft die "extrem Ultraviolett"-Laserquellen so weit gebracht werden, dass sie einsetzbar sind. Die arbeiten dann mit ca. 13nm und damit verschafft man sich wieder ein bischen mehr Luft.

Irgendwann wird man aber auf jeden Fall eine physikalische Grenze erreichen, aber bis dahin gibt es bestimmt die ein oder andere geniale Idee...derzeit schwirrt da ja einiges rum wie Kohlenstoff-Nanotubes oder sogar dem internen Informationsaustausch per Licht, womit Leiterbahnen sowieso der Vergangenheit angehören werden.

Ich werde mich einfach überraschen lassen und freue mich für die beteiligten Firmen, wenn diese Strategie mit den Zwischenschritten aufgeht. Der hört sich zwar nicht so gewaltig an, aber man bekommt schon durch die 4nm wieder eine ganz gute Menge mehr Chips auf einen Wafer und Waferfläche ist auch sehr kostbar, sodass - wenn alles gut läuft - die Entwicklungskosten schon wieder reinkommen sollten. Und der dadurch entstehende Wettbewerbsvorteil sollte wohl nicht zu verachten sein. Wenn die Firmen nicht davon ausgingen würden sie einen solchen aus ökonomischer Sicht wenig sinnvollen Schritt auch nicht machen.

EDIT: Da hab ich doch tatsächlich das Graphen verschwiegen...