Nerevar

Lt. Commander

- Registriert

- März 2006

- Beiträge

- 1.354

ghecko schrieb:Das muss ich mir noch mal genauer anlesen. Ich war der Auffassung, DDR/2 entspricht dem Realtakt auf dem Bus.

https://de.wikipedia.org/wiki/DDR-SDRAM

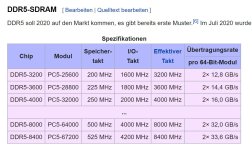

DDR5-8000 hat effektiv 64 GB/s, darum ist die JEDEC Bezeichnung PC5-64000 (also 64000 MB/s). Das finde ich ist die eindeutigste Bezeichnung, weil hier der Marketing-Takt keine Rolle spielt. Der reale Takt der Speicherchips ist bei DDR5-8000 "nur" 500 MHz. Den gleichen realen Speichertakt hat DDR4-4000 Speicher (x8 Prefetch statt x16).

Weil die Latenz ein Maß der Taktzyklen zwischen einem Read/Write und einem Refresh ist und sich dieses Maß auf die Speicherchips bezieht, kann man auch verstehen, warum DDR5 so schlechte Latenzen hat. Denn die Speicherchips laufen nur halb so schnell wie bei DDR4.

Wir dümpeln bei den Latenzen, wenn man diese in Nanosekunden ausdrückt statt Zyklen, seit vielen Jahren im gleichen Bereich um 10ns rum, weil mit (fast) jeder DDRx-SDRAM Version der reale Takt wieder halbiert wird und somit der reale Takt auch immer ungefähr gleich bleibt. Die JEDEC-Specs entsprechen fast immer einer realen Frequenz der Chips von 200 MHz bis maximal 500 MHz.

@Jan @SV3N

darum ist nach meinem Verständnis der Titel des Artikels falsch, bzw. die 4000MHz beziehen sind auf den I/O-Takt von DDR5-8000. Wobei mir nicht ganz klar ist, was dieser I/O-Takt genau aussagt. Hingegen wären 8000 MT/s, 500 MHz Chip-Takt (klingt langweilig) oder 64 GB/s pro Channel die korrekten Angaben.

Edit: es gab ja schon einen passenden Artikel zu der Thematik... dann kann ich die 4000 MHz in der Überschrift noch weniger verstehen

https://www.computerbase.de/artikel...-speicher-latenzen.77142/#abschnitt_ddr5sdram

Anhänge

Zuletzt bearbeitet: