Taxxor schrieb:

Das Infinity Fabric ist einfach eine Art Leiterbahn zwischen den einzelnen Komponenten.

OK, soweit klar

.

Taxxor schrieb:

Das Chiplet besteht nach wie vor aus 2 CCX die per IF verbunden sind.

War ein Denkfehler von mir. Ich dachte, daß Chiplet hat den CCX ersetzt.

Taxxor schrieb:

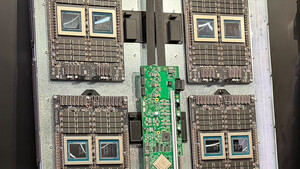

Dieses Chiplet bzw bei den 12/16C dann zwei Chiplets kommunizieren, ebenfalls über den IF, mit dem I/O Die.

Jetzt wirds für mich aber etwas kompliziert, entschuldige

. Wenn ich`s richtig verstanden habe bedeutet das folgendes: Die IF ist sozusagen universell - eine Art Leiterbahn wie du gesagt hast. Und die I/O-Die ist mit dem IF ebenfalls verbunden.

Taxxor schrieb:

Der I/O Die übernimmt, wie der Name schon sagt, die Inputs und Outputs, also die Kommunikation zwischen Cores und z.B. RAM

Also über die (teilweise sehr vielen) CCX eines Zen-Prozessors hinaus. Er überbrückt quasi die bisherigen Flaschenhälse der Zen-Architektur (IF/CCX/RAM). Sozusagen eine Art "overhead" - eine übergeordnete Einheit welche für sämtliche Kommunikationen zwischen IF, den CCXes und dem RAM zuständig ist, richtig?

Taxxor schrieb:

Dieser Part war bei Zen und Zen+ im Zeppelin Die Integriert, die jetzigen chiplets enthalten nur noch die Cores+Cache

Wenn das so ist würde das in meinen Augen bedeuten, daß man z. B. den L3 Cache von Zen2 (beim 8-Kerner) als eine einzige Einheit verstehen kann. Also nicht mehr 2 x 8 MB, sondern direkt 16MB (bzw. 32MB, da sich der Cache bei Zen2 verdoppeln dürfte). Der I/O-Chip sorgt dafür, daß alles eins wird - sehr stark vereinfacht ausgedrückt

.

Uff, ist wirklich kompliziert das ganze.

BTW: Möchte einfach mal Danke sagen, daß ihr soviel Geduld aufbringt mit der Beantwortung meiner (für euch vielleicht) trivialen Fragen

. Ich bewundere wirklich eure Fachkenntnisse was Prozessorarchitektur angeht. Bin ja auch nicht wirklich unwissend - aber hier im Forum gibts schon eine Menge Leute die weitaus mehr wissen als ich

.

Wünsche euch allen ne GuN8!