MK one

Banned

- Registriert

- März 2017

- Beiträge

- 4.889

Nureinnickname! schrieb:2 Stunden Trotz 16 Threads für das Encoding mit H265? Heftig, dachte der CPU wäre schneller. Wie lange braucht denn ein i7 8 Kerner bei den Selben Settings?

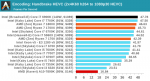

Intel I7 ? 10 min weniger ? - tut sich nicht viel ... , was ich zu den Grafiken unten sagen muss - sie stammen vom 02.03 - seitdem hat sich einiges getan , insbesondere der Ryzen balanced Plan sorgt bei mir unter Handbrake für 2 - 3 Frames mehr die sec ( h264 ). H265 hab ich noch nicht soviel encodiert , erst 2 - 3 Filme um zu sehen wieviel es einspart an Filegrösse , da zur Zeit allerdings nur mein Computer H265 abspielen kann , habe ich aus Kompatibilitätsgründen in h264 encodiert

2 Stunden dauert es nur wenn du einen 2 1/2 Stunden Film hast und in HQ 2 Pass encodierst , kannst das ganze auch in der halben Zeit kriegen mit entsprechenden Qualitätsabstrichen

den 1090T hatte ich vor dem ryzen , kannst ja mal Handbrake runterladen und in HQ encodieren wenn ich mich recht entsinne sind s dann 8 - 12 Stunden oder war s nen ganzer Tag ? ( h265 ) hmmm

http://www.anandtech.com/show/11170/the-amd-zen-and-ryzen-7-review-a-deep-dive-on-1800x-1700x-and-1700/20

Zuletzt bearbeitet: