es geht ja nicht allein um die Masken , es geht auch um Kosten und die Tatsache das 7 nm ein brandneuer Fertigungsprozess ist dessen yield mit zunehmender Chipgröße abnimmt , rechnet man die IO und IMC Anteile wieder rein steigt die Größe des Chips von 64 auf 98 - 105 mm , denn der Cache soll ja auf 32 MB steigen , oder man lässt das beim Desktop weg , dann wären es 92 - 94 mm2 .

Es kommt wirklich darauf an ob ein aktiver Interposer Verwendung findet oder nicht und wie wirkungsvoll dieser ist . Im Grunde ist ein Interposer nichts neues für AMD , er findet bei Vega Anwendung , wenn auch passiv , die HBM Speichermodule werden damit angebunden .

Je kleiner der Chip desto billiger der Interposer , dürften die Kosten bei der 64 Kern CPU bei 60 - 70 Euro liegen kann man man das bei einer 2 Chiplet Variante mit kleinerem IO auf 20 - 25 Euro runterrechnen , im Grunde nicht viel mit Ausname des unteren Mainstreambereichs , und da wird es APU Lösungen geben , möglicherweisese mit 6 oder 8 Kernen , wohl eher 6 , wenn die GPU auch etwas ausgebaut und ein paar CU s mehr haben soll .

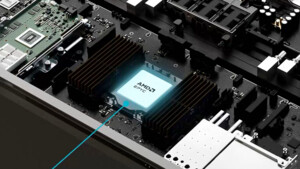

Klar kann es auch eine Desktop Maske geben , jedoch denke ich nach wie vor , das AMD Versuchen wird den Core Count im Mainstream anzuheben auf 12 Kerne meinetwegen um einen weiteren Vorteil gegenüber Intel zu haben , das würde einen Mono Die jedoch weiter vergrößern auf ca 140 mm2 mit entsprechend niedrigerem yield , beim Verwendung von Chiplets mit IO hingegen wäre es kein problem , zweites Chiplet drangeflanscht und gut = 4C, 6C , 8C = 1 Chiplet , 10C , 12C ,14C ,16 C = 2 Chiplets .

Bereits mitte des Jahres war in Luxx dieser Artikel zu finden

https://www.hardwareluxx.de/index.p...-aktivem-interposer-als-emib-gegenstueck.html

AMD forscht an aktivem Interposer als EMIB-Gegenstück

passt wie die Faust auf s Auge , oder ? Denn hat man erst mal die Technik , warum sollte man sie nicht nutzen , zudem man sowieso noch einen Abnahme Zwang gegenüber GloFo hat , warum also nicht 14 nm IO Chips nutzen ? oder kostengünstig 65 nm für den Interposer ?

https://seal.ece.ucsb.edu/sites/sea.../2017-iccad-stow-activepassiveinterposers.pdf

Taniya Siddiqua, Gabriel H. Loh AMD Research Advanced Micro Devices, Inc.

Dylan Stow, Yuan Xie Electrical and Computer Engineering University of California, Santa Barbara

ein aktiver Interposer hat noch einen weiteren Vorteil , die Übertragungsrate kann länger hoch gehalten werden

beim passiven Interposer halbiert sich die Übertragungsrate schon nach 3 mm von 7 auf 3,5 Gbps , beim aktiven nur von 8 Gbps auf 5,5 Gbps

PS: man hat in dem Dokument sogar ne kostenberechnung gemacht , zwei 4 Core Chiplets + 65 nm aktivem Interposer = genauso teuer wie ein monolithic 8C Die ( linkes Diagramm )

was in der Kostenberechnung fehlt ist der System Controllerchip und der ist relativ klein mit 112 mm2 , dürfte rund 60 % der Kosten eines 14nm Ryzen Die s betragen